# **i960® Microprocessor User Guide for Cyclone and PCI-SDK Evaluation Platforms**

**April 1995**

**Order Number: 272577-002**

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions & Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners

Additional copies of this document or other Intel literature may be obtained from

Intel Corporation

Literature Sales

P.O. Box 7641

Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

© INTEL CORPORATION 1995

**CHAPTER 1

INTRODUCTION**

|       |                                                      |     |

|-------|------------------------------------------------------|-----|

| 1.1   | ADVANTAGES AND FEATURES .....                        | 1-2 |

| 1.2   | ABOUT THIS MANUAL .....                              | 1-2 |

| 1.2.1 | Notation Conventions .....                           | 1-3 |

| 1.3   | TECHNICAL SUPPORT, SCHEMATICS AND PLD EQUATIONS..... | 1-3 |

| 1.4   | ADDITIONAL INFORMATION.....                          | 1-4 |

**CHAPTER 2

GETTING STARTED**

|         |                                                              |     |

|---------|--------------------------------------------------------------|-----|

| 2.1     | PRE-INSTALLATION CONSIDERATIONS .....                        | 2-1 |

| 2.1.1   | Software Development Tools .....                             | 2-1 |

| 2.1.2   | MON960 Debug Monitor .....                                   | 2-1 |

| 2.1.3   | Host Communications .....                                    | 2-2 |

| 2.1.3.1 | Terminal Emulation Method .....                              | 2-2 |

| 2.1.3.2 | Host Debugger Interface Library (HDIL) Method .....          | 2-2 |

| 2.1.3.3 | Source Level Debugger .....                                  | 2-2 |

| 2.1.4   | Power Requirements .....                                     | 2-2 |

| 2.2     | SOFTWARE INSTALLATION.....                                   | 2-3 |

| 2.2.1   | Installing Software Development Tools .....                  | 2-3 |

| 2.3     | HARDWARE INSTALLATION .....                                  | 2-3 |

| 2.3.1   | Verify Cyclone EP is Functional .....                        | 2-3 |

| 2.4     | CREATING AND DOWNLOADING THE EXAMPLE PROGRAM .....           | 2-4 |

| 2.4.1   | MONDB.EXE-to-Cyclone EP Communication Support .....          | 2-4 |

| 2.4.2   | Terminal Emulation-to-Cyclone EP Communication Support ..... | 2-6 |

**CHAPTER 3

HARDWARE REFERENCE**

|       |                                         |      |

|-------|-----------------------------------------|------|

| 3.1   | CONNECTORS, SWITCHES AND LEDS .....     | 3-1  |

| 3.2   | CPU MODULES .....                       | 3-3  |

| 3.2.1 | CPU Module Installation .....           | 3-3  |

| 3.2.2 | CPU Module Clock Frequencies .....      | 3-3  |

| 3.2.3 | i960 Jx/Hx CPU Counter/Timers .....     | 3-4  |

| 3.2.4 | CPU Module V <sub>PP</sub> Switch ..... | 3-4  |

| 3.3   | CPU MEMORY MAP .....                    | 3-4  |

| 3.4   | INTERLEAVED DRAM .....                  | 3-5  |

| 3.4.1 | DRAM Performance .....                  | 3-5  |

| 3.4.2 | Upgrading SIMM DRAM .....               | 3-6  |

| 3.5   | FLASH MEMORY .....                      | 3-7  |

| 3.5.1 | SwapROM Switch .....                    | 3-7  |

| 3.6   | INTERRUPTS.....                         | 3-8  |

| 3.7   | CONSOLE SERIAL PORT .....               | 3-9  |

| 3.8   | PARALLEL PORT .....                     | 3-10 |

| 3.8.1 | Parallel Port Bit Assignments .....     | 3-10 |

| 3.9   | Z8536 COUNTER I/O UNIT (CIO).....       | 3-11 |

| 3.9.1 | Counter/Timers .....                    | 3-11 |

| 3.9.2 | CIO Port A .....                        | 3-12 |

| 3.9.3 | CIO Port B .....                        | 3-13 |

## CONTENTS

|          |                                                      |      |

|----------|------------------------------------------------------|------|

| 3.9.4    | CIO Port C .....                                     | 3-14 |

| 3.10     | NON-VOLATILE PARAMETER MEMORY .....                  | 3-14 |

| 3.11     | SQUALL II MODULE INTERFACE .....                     | 3-14 |

| 3.12     | PLX PCI 9060 INTERFACE (PCI-SDK Platform Only) ..... | 3-16 |

| 3.12.1   | PCI 9060 Configuration .....                         | 3-16 |

| 3.12.1.1 | Accessing Configuration Registers .....              | 3-17 |

| 3.12.1.2 | PCI-to-Local Configuration .....                     | 3-18 |

| 3.12.1.3 | RAM Region Configuration .....                       | 3-19 |

| 3.12.1.4 | Expansion ROM Region Configuration .....             | 3-22 |

| 3.12.1.5 | Memory Region Configuration Examples .....           | 3-22 |

| 3.12.2   | Local-to-PCI Configuration .....                     | 3-24 |

| 3.12.3   | Deadlock Configuration .....                         | 3-27 |

| 3.12.4   | Signalling Init Done .....                           | 3-28 |

| 3.12.5   | PCI Interrupts .....                                 | 3-28 |

| 3.12.5.1 | Local PCI Interrupts .....                           | 3-29 |

| 3.12.6   | Mailbox Registers and Doorbell Interrupts .....      | 3-31 |

| 3.12.6.1 | Using the Mailbox Registers .....                    | 3-31 |

| 3.12.6.2 | Generating Doorbell Interrupts .....                 | 3-31 |

| 3.12.6.3 | Receiving Doorbell Interrupts .....                  | 3-31 |

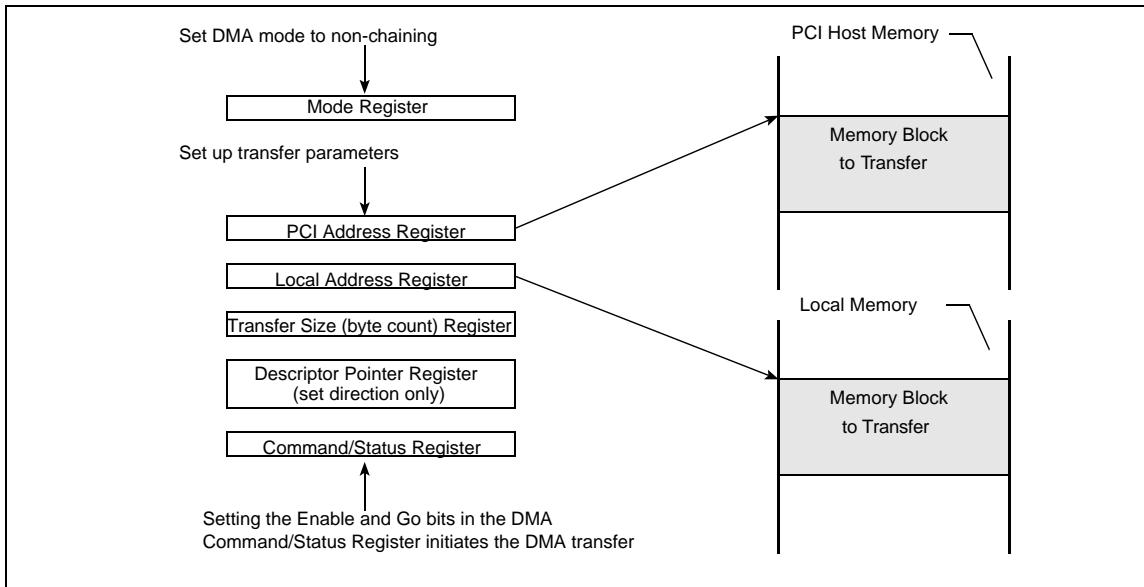

| 3.12.7   | DMA Programming .....                                | 3-32 |

| 3.12.7.1 | DMA Non-Chaining Mode .....                          | 3-32 |

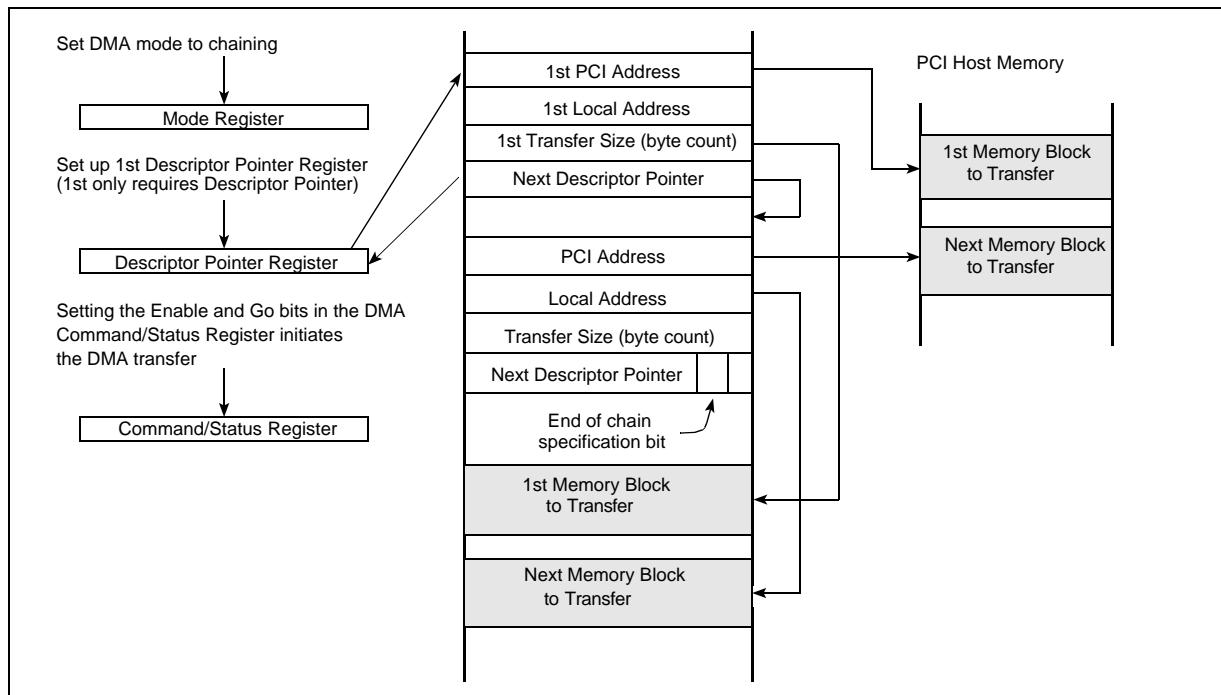

| 3.12.7.2 | DMA Chaining Mode .....                              | 3-33 |

| 3.12.7.3 | DMA Interrupts .....                                 | 3-34 |

## CHAPTER 4 THEORY OF OPERATION

|         |                                      |      |

|---------|--------------------------------------|------|

| 4.1     | FUNCTIONAL OVERVIEW .....            | 4-1  |

| 4.2     | CLOCK GENERATION .....               | 4-1  |

| 4.3     | POWER MONITOR AND RESET .....        | 4-2  |

| 4.4     | I/O INTERFACE .....                  | 4-2  |

| 4.4.1   | Functional Blocks .....              | 4-3  |

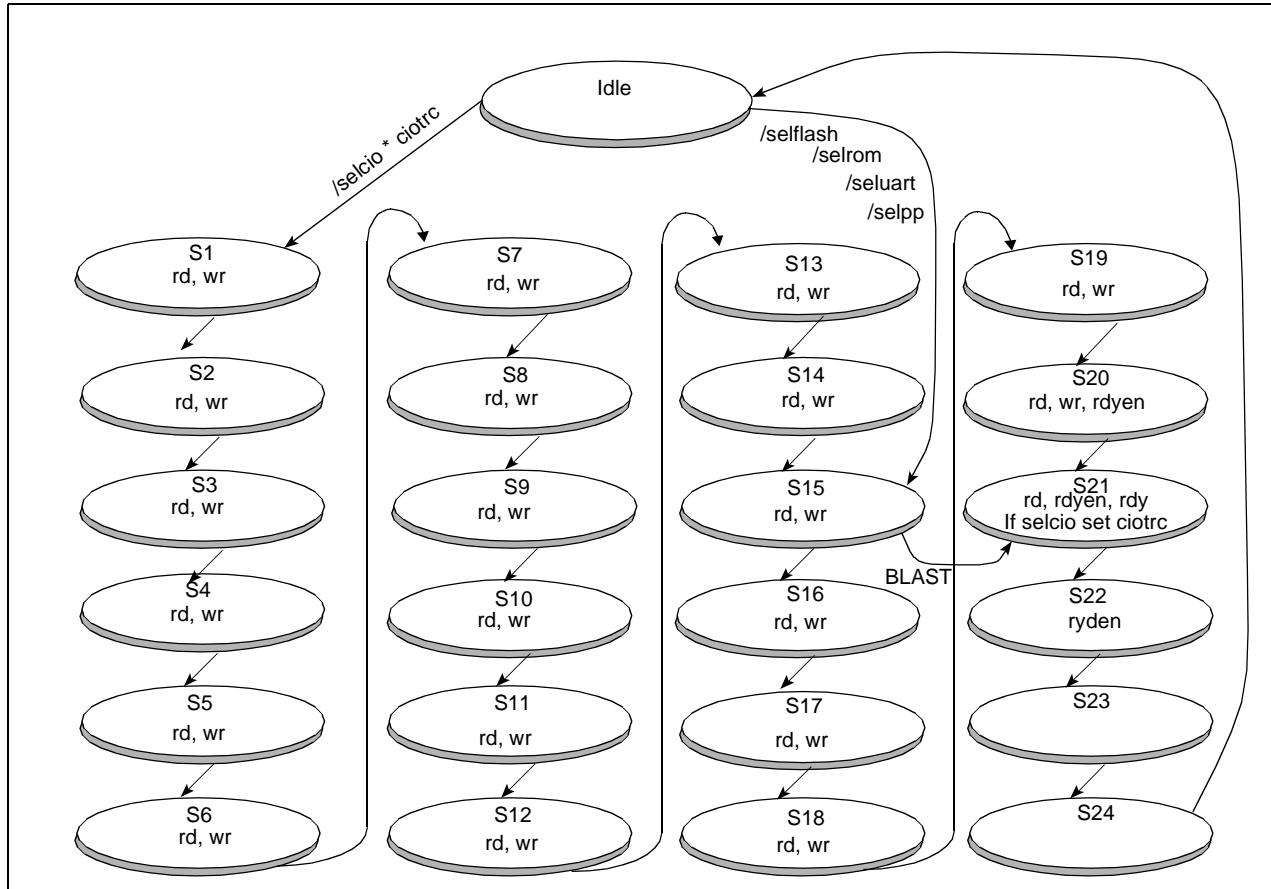

| 4.4.2   | I/O Control Timing .....             | 4-3  |

| 4.4.3   | Data Path .....                      | 4-4  |

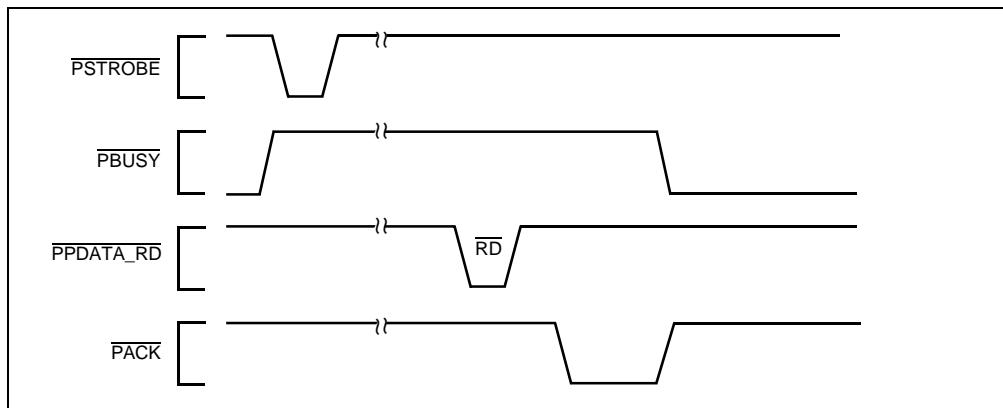

| 4.4.3.1 | Parallel Port .....                  | 4-5  |

| 4.4.3.2 | Serial Port .....                    | 4-6  |

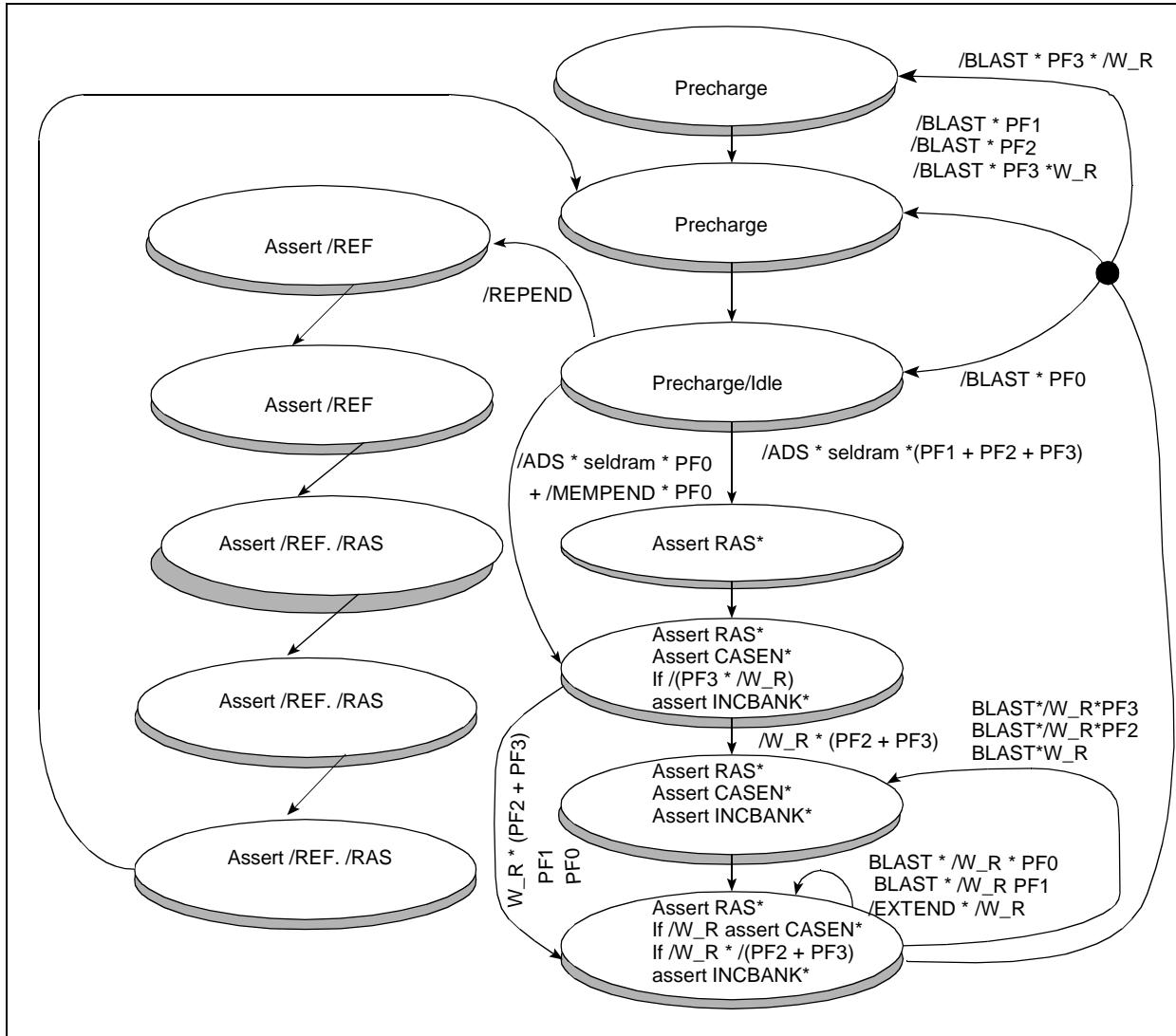

| 4.5     | DRAM SUBSYSTEM .....                 | 4-6  |

| 4.5.1   | Page Mode DRAM SIMM Review .....     | 4-6  |

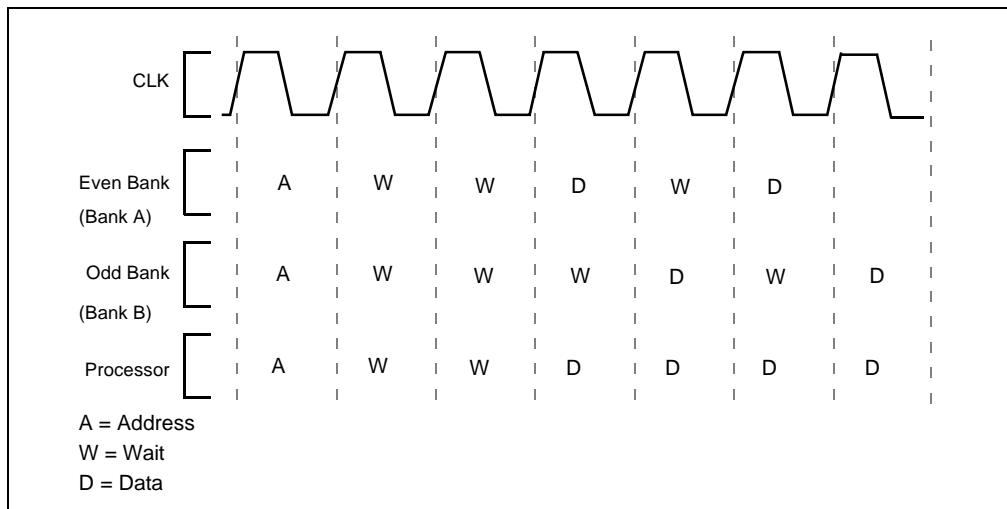

| 4.5.1.1 | Bank Interleaving .....              | 4-7  |

| 4.5.1.2 | Wait State Performance .....         | 4-7  |

| 4.5.2   | DRAM Controller Implementation ..... | 4-8  |

| 4.6     | CAS Generation .....                 | 4-10 |

| 4.7     | Refresh Generation .....             | 4-10 |

**CHAPTER 5**

**SQUALL II MODULE INTERFACE**

|       |                                                           |      |

|-------|-----------------------------------------------------------|------|

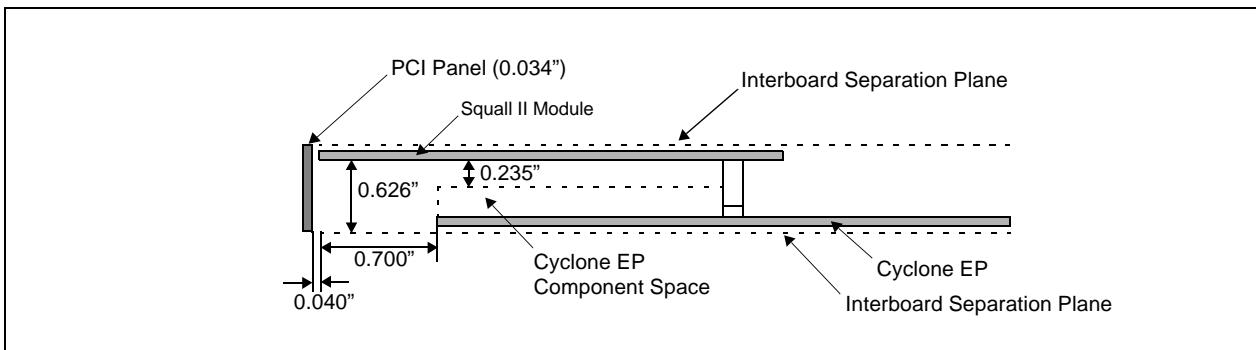

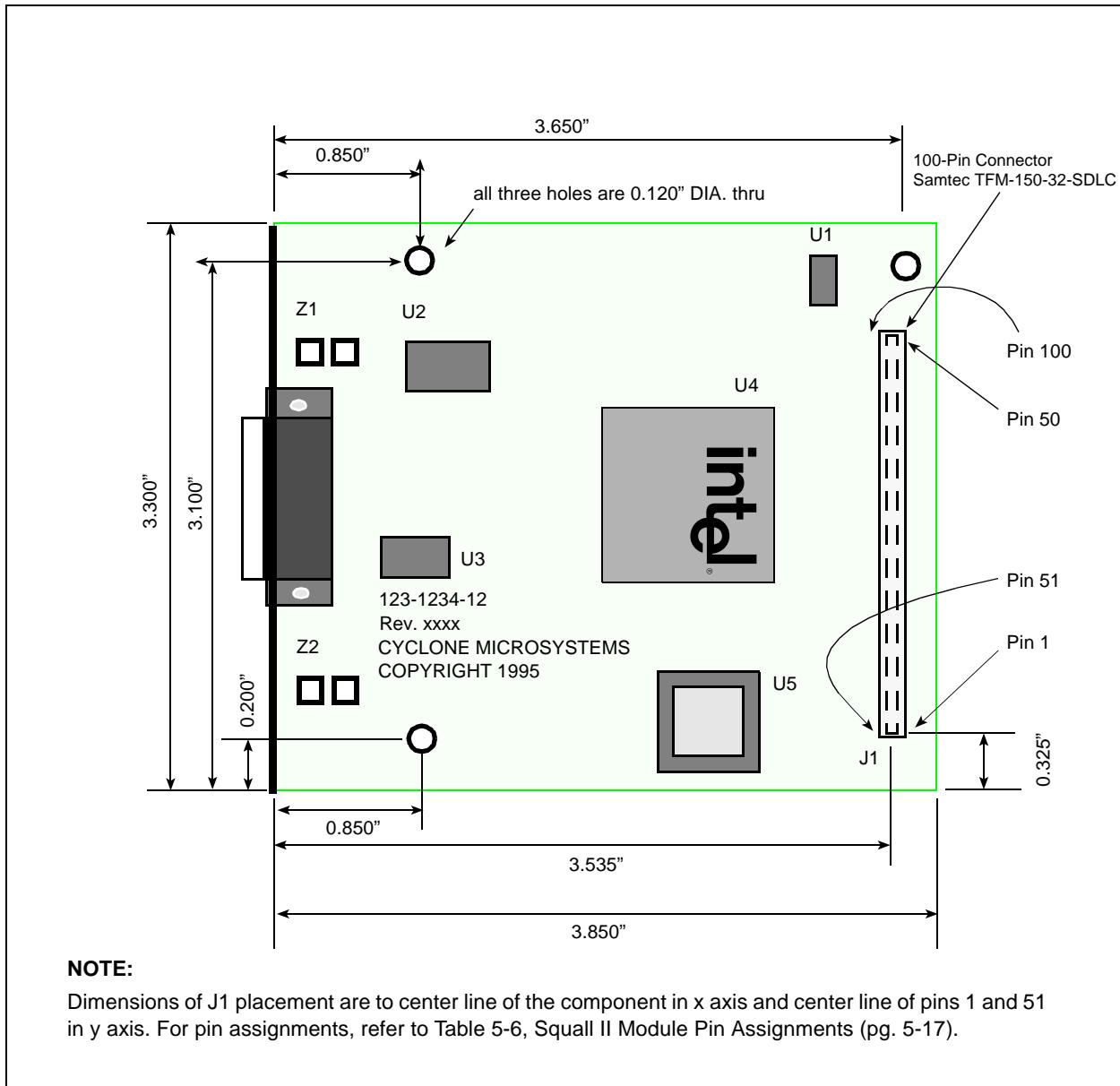

| 5.1   | Physical Attributes .....                                 | 5-1  |

| 5.2   | Power Requirements .....                                  | 5-3  |

| 5.3   | Squall II Module Serial EEPROM .....                      | 5-3  |

| 5.4   | Squall II Module Signal Definitions .....                 | 5-4  |

| 5.5   | Squall Module Signal Descriptions .....                   | 5-5  |

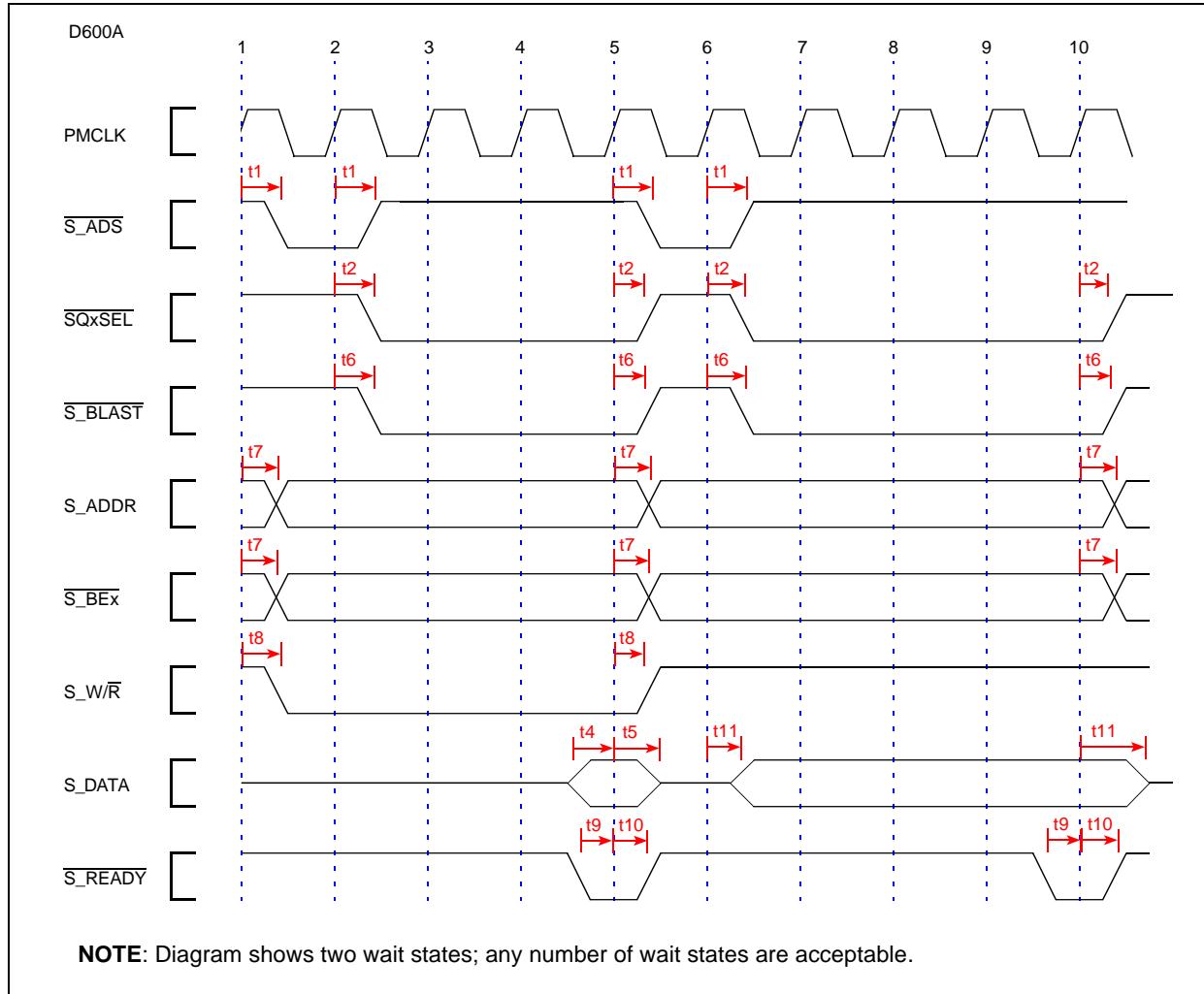

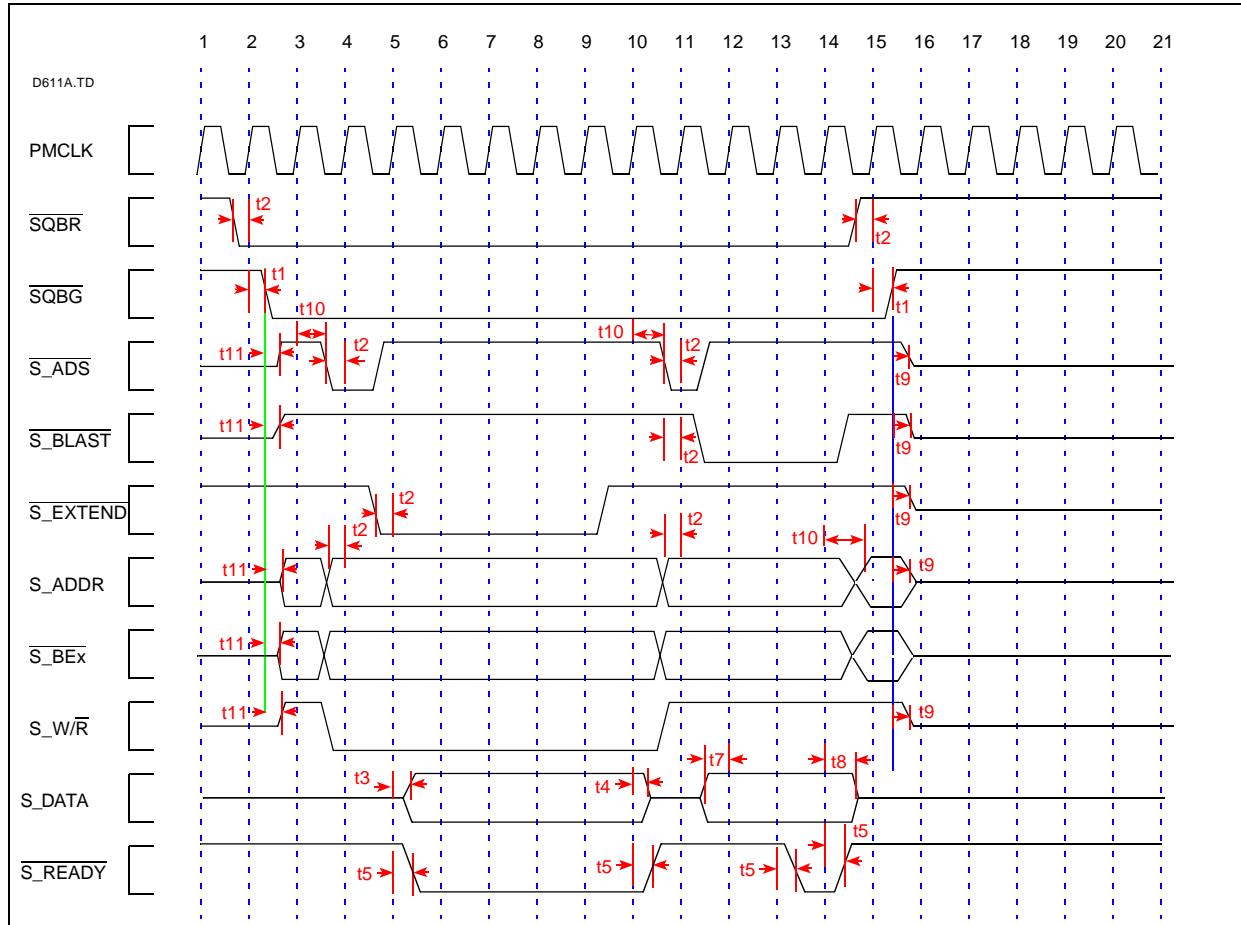

| 5.6   | Squall II Module Timing .....                             | 5-8  |

| 5.6.1 | Squall II Module Slave Timing .....                       | 5-8  |

| 5.6.2 | Squall II Module Master Timing .....                      | 5-12 |

| 5.7   | Squall II Module Connector .....                          | 5-17 |

| 5.8   | Squall II Module Signal Loading and Logic Selection ..... | 5-18 |

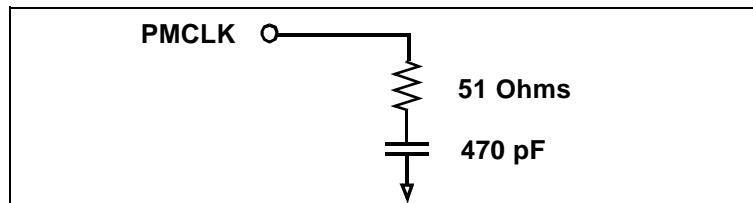

| 5.9   | Squall II Module Clock Termination .....                  | 5-18 |

**APPENDIX A**

**PARTS LIST****FIGURES**

|             |                                                                |      |

|-------------|----------------------------------------------------------------|------|

| Figure 1-1  | Cyclone EP and PCI-SDK Platform Functional Block Diagram ..... | 1-1  |

| Figure 2-1  | Download Messages .....                                        | 2-5  |

| Figure 2-2  | Program Execution Messages .....                               | 2-6  |

| Figure 3-1  | Cyclone EP and PCI-SDK Platform Physical Diagram .....         | 3-1  |

| Figure 3-2  | DRAM Memory Map for Cyclone EP .....                           | 3-5  |

| Figure 3-3  | CIO Port A .....                                               | 3-12 |

| Figure 3-4  | CIO Port B .....                                               | 3-13 |

| Figure 3-5  | CIO Port C .....                                               | 3-14 |

| Figure 3-6  | Non-Chaining DMA Initialization .....                          | 3-33 |

| Figure 3-7  | Chaining DMA Initialization .....                              | 3-34 |

| Figure 4-1  | I/O Control State Machine .....                                | 4-4  |

| Figure 4-2  | Parallel Port Timing Signals .....                             | 4-5  |

| Figure 4-3  | Two-way Interleaving .....                                     | 4-7  |

| Figure 4-4  | DRAM State Machine .....                                       | 4-9  |

| Figure 5-1  | Squall II Module Component Height Allowance .....              | 5-1  |

| Figure 5-2  | Squall II Module Dimensions .....                              | 5-2  |

| Figure 5-3  | Squall II Module EEPROM Memory Map .....                       | 5-4  |

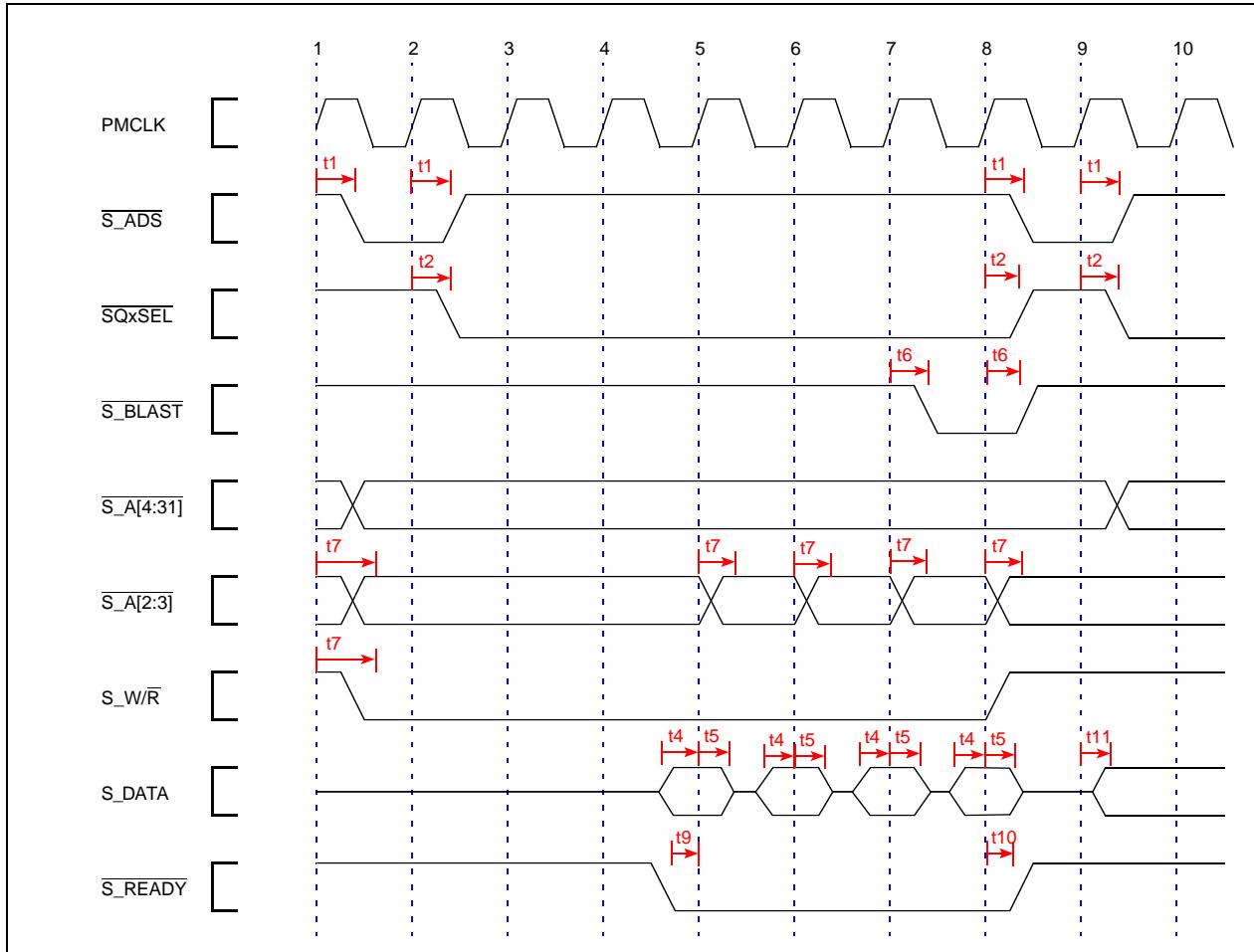

| Figure 5-4  | Squall II Slave Read and Write Timing Diagram .....            | 5-10 |

| Figure 5-5  | Squall II Slave Burst Read Timing Diagram .....                | 5-11 |

| Figure 5-6  | Squall II Slave Burst Write Timing Diagram .....               | 5-12 |

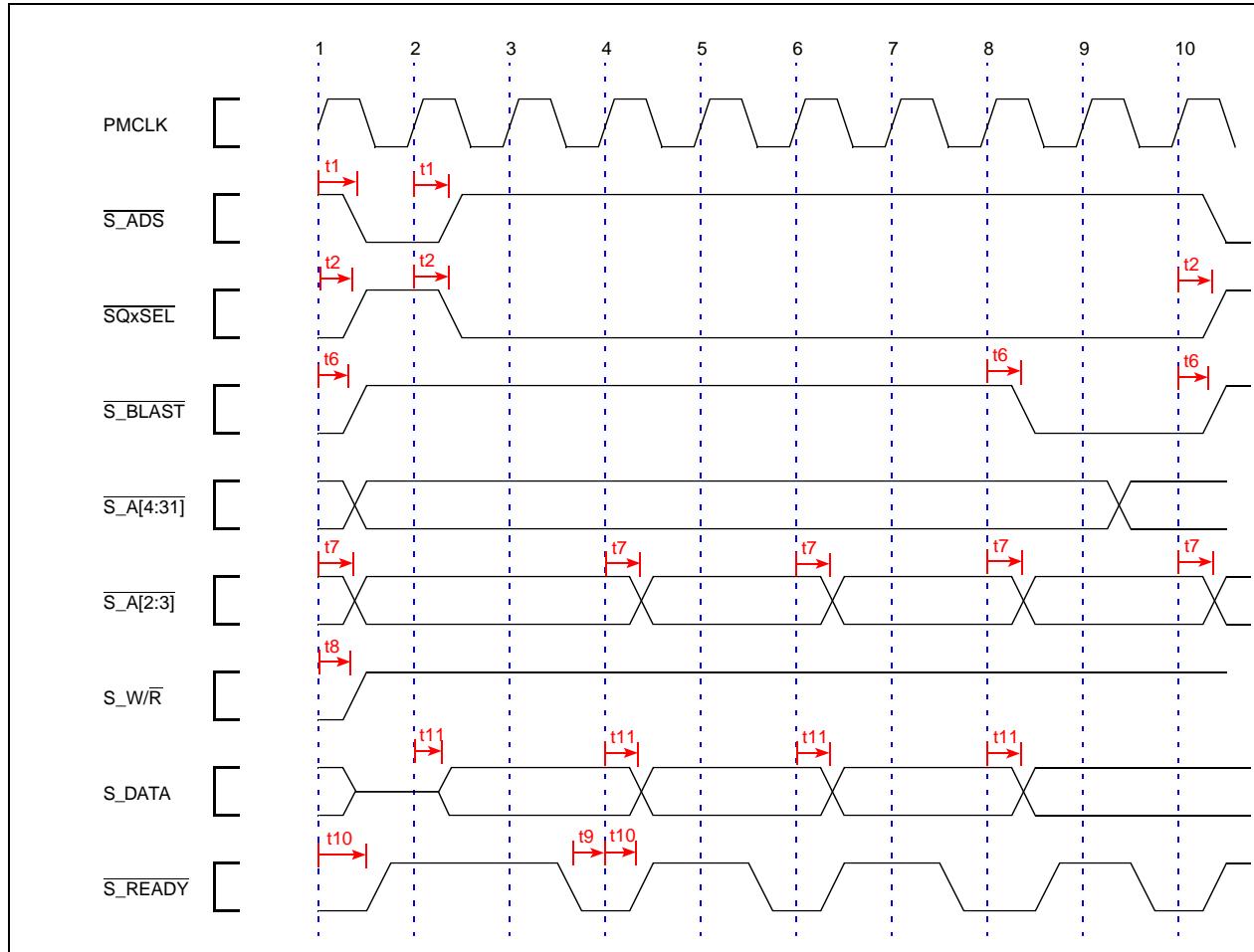

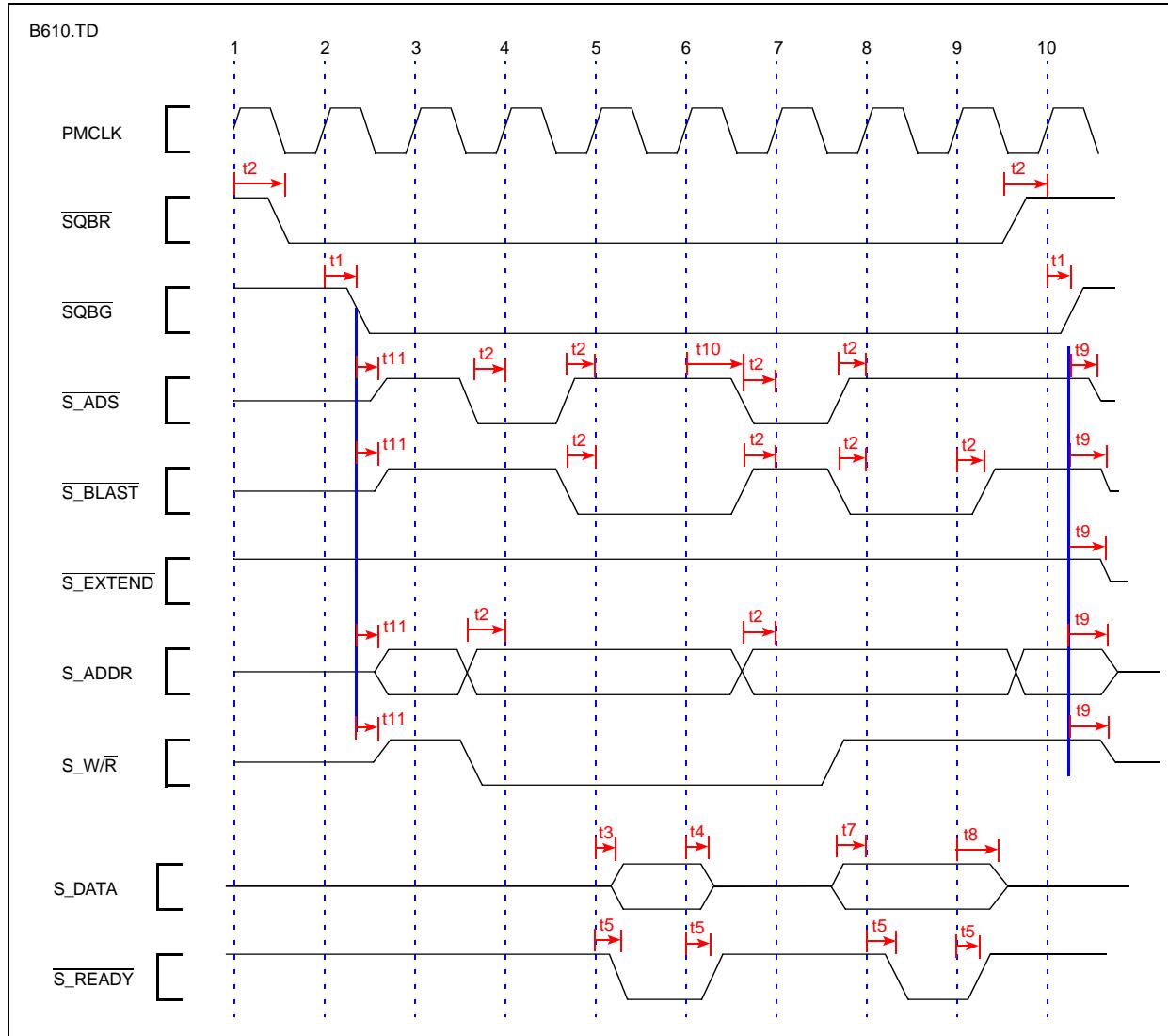

| Figure 5-7  | Squall II Master Read and Write Timing Diagram .....           | 5-14 |

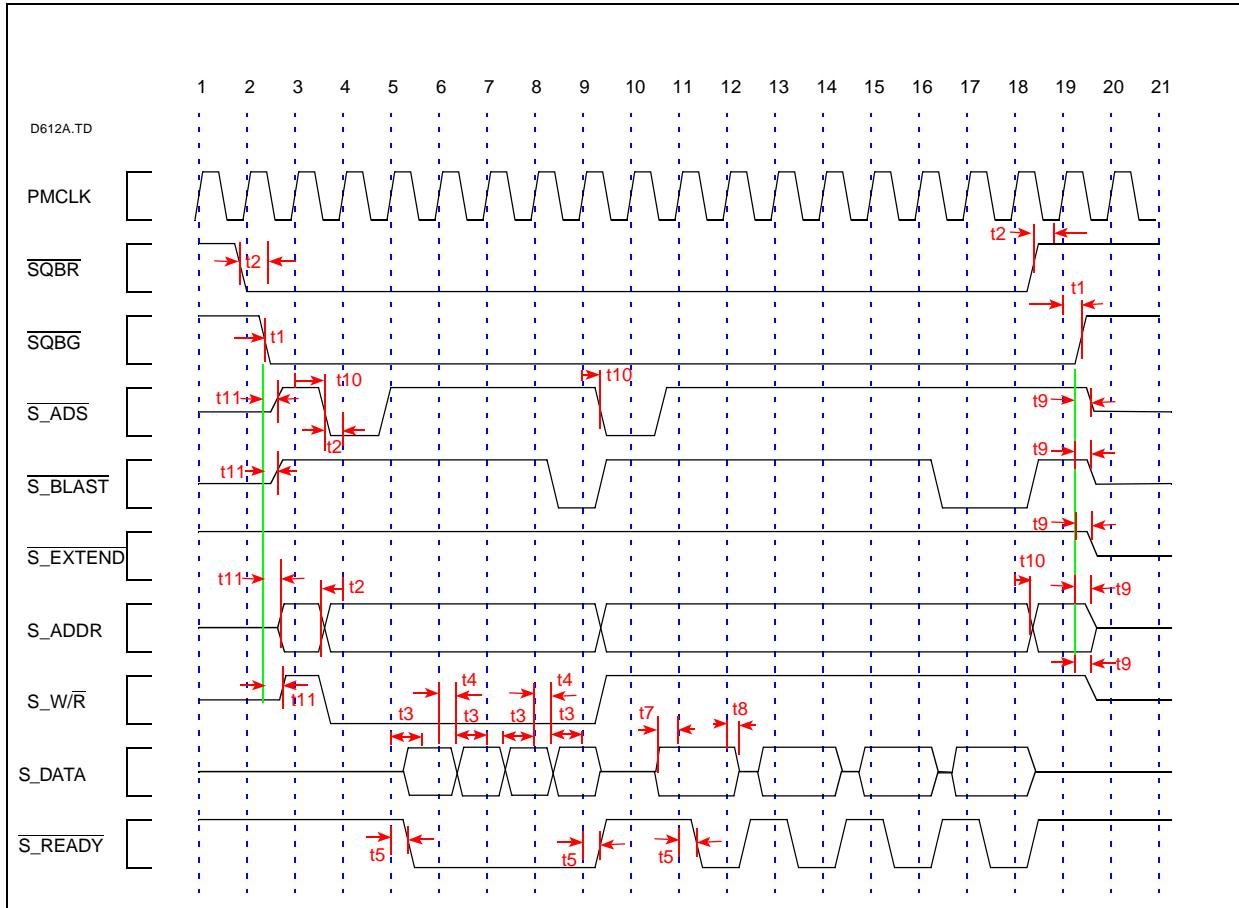

| Figure 5-8  | Squall II Master Burst Read and Write Timing Diagram .....     | 5-15 |

| Figure 5-9  | Squall II Master Read Using <u>S_EXTEND</u> .....              | 5-16 |

| Figure 5-10 | Squall II Module Clock Termination .....                       | 5-18 |

## CONTENTS

### TABLES

|            |                                                                                      |      |

|------------|--------------------------------------------------------------------------------------|------|

| Table 3-1  | External Connectors and LEDs .....                                                   | 3-2  |

| Table 3-2  | CPU Module Frequency Switch Settings.....                                            | 3-3  |

| Table 3-3  | i960 Jx/Hx CPU Clock Rates.....                                                      | 3-4  |

| Table 3-4  | DRAM Access Times.....                                                               | 3-6  |

| Table 3-5  | DRAM SIMM Configurations .....                                                       | 3-7  |

| Table 3-6  | Flash ROM Addresses .....                                                            | 3-7  |

| Table 3-7  | Interrupt Sources .....                                                              | 3-8  |

| Table 3-8  | 80960Sx and Kx Interrupt Sources.....                                                | 3-8  |

| Table 3-9  | 80960Sx and Kx Interrupt Switch Settings .....                                       | 3-9  |

| Table 3-10 | UART Register Addresses .....                                                        | 3-9  |

| Table 3-11 | Parallel Port Addresses .....                                                        | 3-10 |

| Table 3-12 | Parallel Port Status Register Bit Assignments.....                                   | 3-10 |

| Table 3-13 | Parallel Port Control Register Bit Assignments .....                                 | 3-11 |

| Table 3-14 | CIO Register Address.....                                                            | 3-11 |

| Table 3-15 | CIO Port A Bits 5-3 .....                                                            | 3-12 |

| Table 3-16 | CIO Port A Bits 2-0 .....                                                            | 3-13 |

| Table 3-17 | Available Squall II Modules .....                                                    | 3-15 |

| Table 3-18 | Squall Module Compatibility at Maximum CPU Clock Speed (33 MHz) .....                | 3-15 |

| Table 3-19 | Local Configuration Registers .....                                                  | 3-18 |

| Table 3-20 | PCI Configuration Registers .....                                                    | 3-19 |

| Table 3-21 | Memory Region 0 Settings .....                                                       | 3-20 |

| Table 3-22 | Local Address Space 0 Range Register.....                                            | 3-20 |

| Table 3-23 | Local Address Space 0 Local Base Address (Re-map) Register Description .....         | 3-20 |

| Table 3-24 | Local Bus Region Descriptor for PCI-to-Local Access Register Description .....       | 3-21 |

| Table 3-25 | ROM Region Settings.....                                                             | 3-22 |

| Table 3-26 | Local Expansion ROM Local Base Address (Re-map) and BREQo Register Description ..... | 3-23 |

| Table 3-27 | Local Expansion ROM Range Register Description .....                                 | 3-23 |

| Table 3-28 | Local Range Register for Direct Master-to-PCI Description .....                      | 3-25 |

| Table 3-29 | PCI Base Address (Re-map) Register for Direct Master-to-PCI Description .....        | 3-25 |

| Table 3-30 | Local Bus Base Address Register for Direct Master-to-PCI Memory .....                | 3-26 |

| Table 3-31 | Local Base Address for Direct Master-to-PCI IO/CFG Register .....                    | 3-26 |

| Table 3-32 | PCI Configuration Address Register for Direct Master-to-PCI IO/CFG .....             | 3-27 |

| Table 3-33 | Interrupt Control/Status .....                                                       | 3-29 |

| Table 4-1  | DRAM Profiles .....                                                                  | 4-8  |

| Table 5-1  | Power Supply .....                                                                   | 5-3  |

| Table 5-2  | Pin Description Nomenclature .....                                                   | 5-5  |

| Table 5-3  | Squall Module Signal Descriptions .....                                              | 5-5  |

| Table 5-4  | Squall II Module Slave Timing .....                                                  | 5-9  |

| Table 5-5  | Squall II Module Master Timing .....                                                 | 5-13 |

| Table 5-6  | Squall II Module Pin Assignments .....                                               | 5-17 |

| Table 5-7  | Squall II Module Signal Loading .....                                                | 5-18 |

| Table A-1  | Cyclone EP/PCI-SDK Platform Bill Of Materials.....                                   | A-1  |

## CONTENTS

CONTENTS

# INDEX

**B**

Bandwidths 3-6

baud rates

on the serial port 3-9

**C**

Centronics interface 4-5

chip selects 4-3

CIO 3-11

specific usage 3-11

C-language compilers 2-1

Clock Generation 4-1

Clock Signals 4-1

Column Address Strobes 4-7

Console Serial Port 3-9

console serial port 3-9

Counter I/O Unit (CIO) 3-11

CPU module

installation 3-3

memory map 3-4

VPP switch 3-4

**D**

data signals 4-4

DB960 2-1

deadlock 3-27

debug monitor (MON960) 2-1

Dedicated Interrupt Signals 3-8

DMA chaining mode 3-33

DMA Channel non-chaining mode 3-32

DMA Channel programming 3-32

DMA controller 3-5

DMA Transfer Size Register 3-32

doorbell registers 3-31

DOS support 2-1

**DRAM**

burst buses 4-6

early write cycles 4-6

features 4-1, 4-6

interleaved 3-5

page mode 4-6

performance 3-6

upgrading SIMMs 3-6

wait state performance 4-7

**DRAM controller** 4-8

**DRAM design**

performance 4-7

SIMMs 3-6

**DRAM Memory** 3-5**DRAM Speed** 3-6**Driver/Receiver, RS-232** 4-6**E****EEPROM Memory** 3-14

**EPROM**

support for 4-1

**Expansion Bus (X-Bus)** 3-2**Expansion ROM** 3-7**F**

**Features**

functional blocks 4-1

I/O design 4-2

modem support 4-6

**FLASH**

programming voltage 2-2

support for 4-1

**Flash memory** 3-7**Flex Logic** 4-8**G****GDB960** 2-1**GNU/960** 2-1

**H**

HDIL 2-1

Host communications 2-2

Host Debugger Interface Library (HDIL) 2-1

**I**

I/O data buffer control 4-3

I/O subsystem

features 4-1

interleaved DRAM 3-5

Interleaving 4-7

Interrupt Control and Status Register 3-28

interrupts 3-8

**L**

LED (RED, GREEN) 3-2

LEDs

power (green) 4-2

LEDs, user 3-2

Local Configuration Registers 3-16

Local DMA Registers 3-16

Local Init Status bit 3-28

**M**

Mailbox registers 3-31

MAX232 4-6

memory system performance 4-7

MON960 2-1

MONDB.EXE utility 2-1

**O**

operating systems

DOS and UNIX 2-1

**P**

parallel port

bit assignments 3-10

control register bit assignments 3-11

data lines 4-5

handshaking lines 4-5

interrupts 4-5

timing relationships 4-5

Parallel Port (Centronics-compatible) 3-2

Parallel port control register 3-10, 4-5

Parallel port data register 3-10, 4-5

parallel port interrupt 3-10

parallel port interrupt enable bit 3-10

Parallel port status register 3-10, 4-5

PCI Configuration Registers 3-16

PCI interrupts 3-28

peripheral I/O 4-4

PINTEN 3-10

PLL, Internal 4-1

Power (+5 VDC) 3-2

Power (+5 VDC, +12 VDC) 3-2

Presence Detect Signals 3-7

**R**

reset push-button 4-2

Reset Strobe 4-2

RS-232 port 3-9

**S**

serial port 4-6

interface 4-6

TXD, RXD, CTS, RTS 4-6

Serial Port (RS-232) 3-2

serial port configuration 2-2

Shared Run Time Registers 3-16

SIMM 3-6

SIMM sockets 3-5

SIMMs 3-6, 4-6

types supported 3-6

Six-position DIP Switch 3-2

Software Development Tools 2-1

source-level debuggers 2-1

Squall 5-2, 5-4, 5-18

Squall II Module, Clock Termination 5-18

Squall II Module, Interrupts 5-3

Squall II Module, Master Timing 5-12

Squall II Module, Physical Dimensions 5-1

Squall II Module, Pin Assignments 5-17

Squall II Module, Programmable Logic 5-18

Squall II Module, Serial EEPROM 5-1

Squall II Module, Signal Descriptions 5-5

Squall II Module, Signal Loading 5-18

Squall II Module, Slave Timing 5-8

SwapROM switch 3-7

## T

terminal emulation 2-2

## U

UART 4-6

Universal Asynchronous Receiver/Transmitter (UART)

4-6

UNIX support 2-1

## V

VPP switch 3-4

Vpp Switch 3-4

## W

wait state performance 4-7

wait states 3-5, 4-6

waveforms 4-8

## X

X-Bus

features 4-1

X-Bus enabled mode 3-10

## Z

Z8536 device (CIO) 3-11

1

# INTRODUCTION

## CHAPTER 1 INTRODUCTION

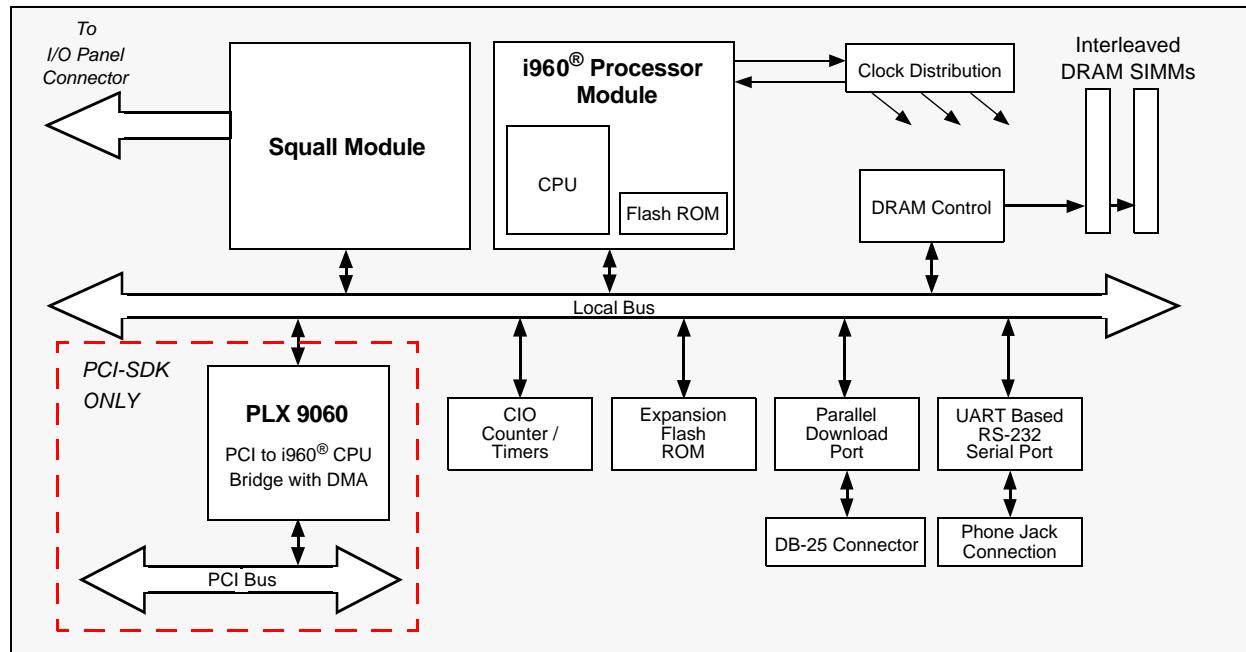

This user's guide describes the Cyclone evaluation platforms for Intel's family of i960® embedded processors:

- Cyclone EP — a standalone general purpose evaluation and development tool.

- PCI-SDK Platform — Cyclone EP equipped with a PCI bus interface. Part of Intel's PCI I/O Software Development Toolkit (SDK).

Both platforms allow you to connect one of several i960 CPU and Squall\* modules. Using the different CPU modules, you can evaluate the various i960 processors in a system environment, or "benchmark" the performance of the various processors.

The PCI-SDK Platform — otherwise identical to the Cyclone EP — is equipped with PLX Technology's PCI 9060 (a PCI to 80960 bus bridge chip). The single-chip PCI 9060 features mailbox and doorbell registers that allow command and status information to pass between PCI bus devices and local bus devices. It can also generate PCI configuration cycles, which enables the PCI 9060 to become the PCI system host.

Unless otherwise noted, all references in this manual to "Cyclone EP" also apply to the PCI-SDK Platform. References that are specific to PCI-SDK Platform are clearly indicated.

Figure 1-1. Cyclone EP and PCI-SDK Platform Functional Block Diagram

### **1.1 ADVANTAGES AND FEATURES**

As shown in Figure 1-1 and Figure 3-1, Cyclone EP and PCI-SDK Platform Physical Diagram (pg. 3-1), the features which make the Cyclone EP useful for evaluation and code development are:

- Interchangeable i960 processor modules (referred to as CPU modules)

- SIMM sockets which support 2, 8, or 32 Mbytes of DRAM

- Flash ROM sockets

- Three 16-bit counter/timers or one 32-bit and one 16-bit counter

- Squall II Module I/O expansion interface

- DIP switch selectable processor clock frequency

- DRAM controller automatically optimizes wait states to CPU frequency and memory speed

- RS-232 serial port

- Parallel download port (Centronics compatible)

- PCI Bus Interface (PCI-SDK Platform only)

### **1.2 ABOUT THIS MANUAL**

This manual contains five chapters, one appendix and an index. A brief description of each follows:

|                                              |                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Chapter 1, INTRODUCTION</b>               | Introduces Intel's Cyclone Evaluation Platform and its features. Also defines notation conventions and related documentation.                                                                                                                                                                                                                              |

| <b>Chapter 2, GETTING STARTED</b>            | In this chapter, step-by-step instructions show you how to connect the Cyclone EP to a power supply and download and execute an example program. This chapter describes Intel's software development tools, the MON960 Debug Monitor, software installation and hardware configuration.                                                                    |

| <b>Chapter 3, HARDWARE REFERENCE</b>         | The location of the CPU and Squall modules, connectors, switches, and LEDs are described in this chapter. Also covered are the memory maps, I/O and memory operation. For the PCI-SDK Platform, this chapter describes the PCI 9060 interface and operation.                                                                                               |

| <b>Chapter 4, THEORY OF OPERATION</b>        | This chapter describes functionality of the Cyclone Evaluation Platform's subsystems. Section 4.4, I/O INTERFACE describes the general I/O implementation. Subsections further describe each functional block. Section 4.5, DRAM SUBSYSTEM similarly defines the DRAM implementation. Also covered are Clock Generation, Reset, Interrupt and Ready Logic. |

| <b>Chapter 5, SQUALL II MODULE INTERFACE</b> | Design information, electrical and physical specifications of the Squall II Module interface are described in this chapter. This information is useful when you wish to design and integrate your own Squall Modules. If you are using a standard Squall Module, refer to the specific module's manual for information on the operation of that module.    |

| <b>APPENDIX A, PARTS LIST</b>                | This appendix identifies Cyclone Evaluation Platform components and quantities, component reference name as it appears on the PC board, description of size or rating and the manufacturer's part number. To order replacement parts contact the manufacturer listed in Table A-1.                                                                         |

### 1.2.1 Notation Conventions

|                              |                                                                                                                                                                                                                                    |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hexadecimal Numbers          | In text, hexadecimal numbers are shown with a suffix of "H" (e.g., XXXX XXXXH). In code examples and PLD files, and in text that refers to specific code examples, hex numbers are shown with a prefix of "0x" (e.g., 0xFFFFFFFF). |

| <u>OVERBAR</u> and #         | Normally inverted <u>clock</u> signals are indicated with an overbar above the signal name (e.g., <u>RAS</u> ). In code examples, such signals are indicated with a trailing pound sign (RAS#).                                    |

| <b>Bold</b>                  | Indicates user entry and/or commands.                                                                                                                                                                                              |

| <i>Italics</i>               | Indicates a reference to related documents; also used to show emphasis.                                                                                                                                                            |

| <code>typewriter font</code> | Indicates code examples and file directories and names.                                                                                                                                                                            |

| asterisks                    | On non-Intel company and product names, a trailing asterisk indicates the item is a trademark or registered trademark. Such brands and names are the property of their respective owners.                                          |

## 1.3

### TECHNICAL SUPPORT, SCHEMATICS AND PLD EQUATIONS

For Technical assistance with the Cyclone EP, contact the Intel Technical Support Hotline. For information about technical support in other geographical areas, contact Intel's North America Technical Support Hotline.

You can also use your PC with modem to download Cyclone EP and PCI-SDK Platform schematics and PLD equations from Intel's Bulletin Board Service (BBS).

|                                                                                 |                                                                                                           |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| <b>Intel Technical Support Hotline</b>                                          | <i>North America:</i> 800-628-8686<br><i>Europe:</i> 44-793-696-000                                       |

| <b>Intel's Bulletin Board Service (BBS)</b><br>for schematics and PLD equations | <i>North America:</i> 916-356-3600<br>supports up to 14.4 Kbps (n,8,1,p)<br><i>Europe:</i> 44-793-432-955 |

## INTRODUCTION

### 1.4 ADDITIONAL INFORMATION

To order manuals from Intel, contact your local sales representative or Intel Literature Sales (1-800-879-4683).

| Product | Document Name                                                                                                     | Company / Order #                |

|---------|-------------------------------------------------------------------------------------------------------------------|----------------------------------|

| All     | Intel Solutions960® catalog                                                                                       | Intel 270791                     |

| 80960Cx | <i>i960® Cx Microprocessor User's Manual</i>                                                                      | Intel 270710                     |

|         | <i>80960CA-33, -25, -16 32-Bit High Performance Embedded Processor Data Sheet</i>                                 | Intel 270727                     |

|         | <i>80960CF-33, -25, -16 32-Bit High Performance Superscalar Processor Data Sheet</i>                              | Intel 272187                     |

|         | <i>80960CF-40 32-Bit High Performance Superscalar Processor Data Sheet</i>                                        | Intel 272493                     |

| 80960Jx | <i>i960® Jx Microprocessor User's Manual</i>                                                                      | Intel 272483                     |

|         | <i>80960JA/JF Embedded 32-Bit Microprocessor Data Sheet</i>                                                       | Intel 272504                     |

| 80960Kx | <i>i960® KA/KB Microprocessor Programmer's Reference Manual</i>                                                   | Intel 270567                     |

|         | <i>80960KB Hardware Designer's Reference Manual</i>                                                               | Intel 270564                     |

|         | <i>80960KA Embedded 32-Bit Processor Data Sheet</i>                                                               | Intel 270775                     |

|         | <i>80960KB Embedded 32-Bit Processor With Integrated Floating Point Unit Data Sheet</i>                           | Intel 270565                     |

| 80960Sx | <i>i960® SA/SB Microprocessor Reference Manual</i>                                                                | Intel 270929                     |

|         | <i>80960SA Embedded 32-Bit Processor With 16-Bit Burst Data Bus Data Sheet</i>                                    | Intel 272206                     |

|         | <i>80960SB Embedded 32-Bit Processor With 16-Bit Burst Data Bus and Integrated Floating Point Unit Data Sheet</i> | Intel 272207                     |

| Other   | <i>MON960 Debug Monitor User's Guide</i>                                                                          | Intel 484290                     |

|         | <i>Z8536 C/I/O Counter/Timer Technical Manual</i>                                                                 | Zilog, Inc.                      |

|         | <i>16C550 Data Sheet</i>                                                                                          | Texas Instruments                |

|         | <i>24C08 Serial EEPROM Data Sheet</i>                                                                             | Xicor, Inc.                      |

|         | <i>Data Communications Local Area Networks UARTs Handbook</i>                                                     | National Semiconductor           |

|         | <i>PCI 9060 User's Guide / Data Sheet</i>                                                                         | PLX Technology<br>(800-759-3735) |

To contact Cyclone Microsystems for additional information about their products:

|                                                               |                     |

|---------------------------------------------------------------|---------------------|

| Cyclone Microsystems<br>25 Science Park<br>New Haven CT 06511 | Phone: 203-786-5536 |

|                                                               | FAX: 203-786-5025   |

2

## GETTING STARTED

## CHAPTER 2 GETTING STARTED

In this chapter, step-by-step instructions show you how to connect the Cyclone EP to a power supply and download and execute an example program. This chapter describes Intel's software development tools, the MON960 Debug Monitor, software installation and hardware configuration.

### 2.1 PRE-INSTALLATION CONSIDERATIONS

This section provides a general overview of the components required to develop and execute a program on the Cyclone EP. The *MON960 Debug Monitor User's Guide* (order number 484290) fully describes several of these components, including MON960 commands, Host Debugger Interface Library (HDIL) and the MONDB.EXE utility.

#### 2.1.1 Software Development Tools

The Cyclone EP supports many software development tools<sup>1</sup>. The installation instructions presented in this chapter were verified using GNU/960 and CTOOLS960 — Intel's i960® processor software development tools. Advanced C-language compilers for the i960 processor family are available for DOS-based systems and a variety of UNIX workstation hosts. These products provide execution profiling and instruction scheduling optimizations and also provide an assembler, linker and utilities designed for embedded processor software development.

The instructions in this section explain how to compile, link and execute an example program. If you are using other software development tools, read through this example to gain a general understanding of how to use your tools with this board.

#### 2.1.2 MON960 Debug Monitor

The Cyclone EP is equipped with Intel's MON960 — an on-board software monitor which allows you to execute and debug programs written for i960 processors. The monitor provides program download, breakpoint, single step, memory display and other useful functions for running and debugging a program.

The Cyclone EP works with source-level debuggers, such as the DB960 and GDB960. The source-level debugger must support the Host Debugger Interface Library (HDIL) defined by MON960.

---

1. Refer to Intel's *Solutions960®* catalog for a complete list of i960 processor software development and debug tools.

### **2.1.3 Host Communications**

MON960 allows you to communicate and download programs developed for the Cyclone EP across a PC's serial, parallel, or PCI interface and a UNIX workstation's serial interface. The Cyclone EP supports two methods: Terminal emulation and Host Debugger Interface Library (HDIL).

#### **2.1.3.1 Terminal Emulation Method**

Terminal emulation software on your system communicates to MON960 on the Cyclone EP via an RS-232 serial port. Serial downloads via terminal emulation require an intelligent host computer that supports XMODEM (a standard transfer protocol). General system requirements are:

- DOS-based computer with PROCOMM\*, CROSSTALK\* or other telecommunication programs

- UNIX\* workstation with an external serial port (e.g., SUN\*)

Configure the serial port for 1200-115200 baud, 8 bits, one stop bit, no parity.

#### **2.1.3.2 Host Debugger Interface Library (HDIL) Method**

The MONDB.EXE utility, provided with MON960, allows you to download, execute and debug an application program on the Cyclone EP. This utility differs from standard terminal emulation programs in that it allows you to download executable images through a serial or parallel port, or via the PCI bus. When using the serial port, the MONDB.EXE utility supports the standard baud rates (from 1200 to 115200 baud) to communicate and download to the Cyclone EP. Downloading via either the parallel port or PCI bus is typically much faster than a serial port; actual performance depends on your system's hardware capabilities. Refer to *MON960 Debug Monitor User's Guide* for detailed information.

#### **2.1.3.3 Source Level Debugger**

You may use a source-level debugger, such as Intel's DB960, GDB960 or other, to establish serial communications with the Cyclone EP. The MON960 Host Debugger Interface Library (HDIL) provides the interface between MON960 and these types of debuggers.

### **2.1.4 Power Requirements**

The Cyclone EP requires a stable power source of at least 3.5 A at +5 VDC. The included power supply meets these requirements and connects to J7. If a card is designed for the expansion bus which requires more than 1.0 A, you need to obtain a suitable power supply. To program FLASH devices, you must supply a FLASH programming voltage through J6. J6 uses a standard PC-AT power connector pinout that provides +5 VDC and +12 VDC to the board. J7 provides +5 VDC only. See Figure 3-1, Cyclone EP and PCI-SDK Platform Physical Diagram (pg. 3-1), for J6, J7 locations.

The PCI-SDK Platform draws power from the PCI bus; it does not require an external power source. The PCI bus also provides the voltages needed for FLASH programming.

## 2.2 SOFTWARE INSTALLATION

### 2.2.1 Installing Software Development Tools

If you haven't done so already, install your development software (CTOOLS960, GNU/960 or other) as described in their respective manuals. All further references to CTOOLS960 or GNU/960 assume the default directories in the respective installation program were selected. You must install the tools before you run the example program as described in Section 2.4, CREATING AND DOWNLOADING THE EXAMPLE PROGRAM.

The example program provided on the MON960 diskette enables you to use CTOOLS960 or GNU/960 (or other) to compile a sample application program. If you are using other software tools, these instructions generally apply; however, in some steps you will need to refer to their respective manuals for compatible commands.

## 2.3 HARDWARE INSTALLATION

Follow these instructions to get your new Cyclone EP running. Be sure you have all items listed on the checklist provided with your Cyclone Evaluation Platform.

### 2.3.1 Verify Cyclone EP is Functional

#### **WARNING :**

MAKE SURE YOU ARE GROUNDED BEFORE REMOVING THE ANTI-STATIC BAG.

OTHERWISE, SEVERE DAMAGE MAY OCCUR TO THE BOARD

1. Visually inspect the board for any damage that may have occurred during shipment. If there are visible defects, return the board for replacement.

2. Place the board in a static-free area; always take precautions to minimize static electricity.

3. Verify that an i960 processor module is installed.

4. Verify that the SwapROM switch (S1 position 3) DIP switch is set to OFF.

5. To install the PCI-SDK Platform in a host system PCI slot, follow the manufacturer's instructions for opening the host system and installing an expansion board in a PCI slot.

6. Serial port connection for communicating and downloading: connect the RS-232 cable — the "phone cord" — from an appropriate port (COM1 or COM2 on a PC) to J5 on the Cyclone EP. Your system has either a DB-9 (9-pin) or a DB-25 (25-pin) connector for its RS-232 port. Both 9-pin and 25-pin connectors are provided.

7. Parallel port connection (optional if using MONDB.EXE) for downloading: connect a 25-pin to 25-pin parallel port cable from an appropriate port (LPT1 or LPT2 on a PC) to J1 on the Cyclone EP.

8. Power supply connections (not required for the PCI-SDK Platform): the Cyclone EP has two power connectors: J6 and J7. Refer to Section 2.1.4, Power Requirements (pg. 2-2) for a description of these connectors; see Figure 3-1, Cyclone EP and PCI-SDK Platform Physical Diagram (pg. 3-1) to verify locations.

**WARNING :**

FAILURE TO PROPERLY CONNECT THE POWER CABLE COULD RESULT IN SEVERE DAMAGE TO THE BOARD.

If using the power supply provided with the Cyclone EP, plug the power supply cable into connector J7. The power supply operates with 120 VAC @ 60 Hz.

If using a power supply that provides +5 VDC, +12 VDC and ground (supply not provided), plug the power supply cable into connector J6.

The PCI-SDK Platform draws power from the PCI bus and should not be connected to an external power supply.

9. Check for power within tolerance. The +5V and +3.3V LEDs should be lit. The -12V and +12V power sources are optional on the standalone board, but should be lit when a PCI-SDK Platform is installed in a PCI slot.

Upon power up the Fail LED should turn OFF, indicating the processor has passed its self test. The green Run LED should light, indicating that the processor is performing bus cycles.

## 2.4

### CREATING AND DOWNLOADING THE EXAMPLE PROGRAM

When you install MON960 on DOS, a text file (ZZ\EXAMPLE\CYCLONE\IMAGE.TXT) describes how to compile, assemble and link the example program. The text file describes how to create the executable image. For this example, the image file is named SIEVE.XX ("XX" is either Cx, Hx, Jx, Kx, or Sx, depending on which CPU module you are using).

If you are using MONDB.EXE on DOS to communicate with the Cyclone EP, continue to Section 2.4.1. If using a terminal emulation program, proceed to Section 2.4.2, Terminal Emulation-to-Cyclone EP Communication Support (pg. 2-6).

#### 2.4.1

##### MONDB.EXE-to-Cyclone EP Communication Support

To invoke the MONDB.EXE utility and download your application program: make sure you are in the ..\CYCLONE directory and, at the DOS prompt, enter DWNLD followed by the name of the image file (filename is not case sensitive). For example, for the Cx CPU module, enter:

**DWNLD SIEVE.C X**

DWNLD invokes a batch file (DWNLD.BAT) which contains MONDB.EXE commands which configure serial port 1, parallel port 1, and set the baud rate to 19200. You can use a text editor to modify this batch file such that it is correct for your system's configuration. Refer to *MON960 Debug Monitor User's Guide* for a description of all commands.

Figure 2-1 shows the messages that display during the download. If using the serial port, the download time increases depending on the baud rate.

```

Section 0, name .text, address 0xA0008000, size 0x6a9c, flags 0x20

writing section at 0xA0008000

Section 1, name .data, address 0xA000ea9c, size 0x4, flags 0x40

writing section at 0xA000ea9c

Section 2, name .bss, address 0xA000ea90, size 0x6d0, flags 0x80 -- noload

Download stats 0.050 sec elapsed, 545920 bytes/sec (533.3Kb/sec)

Starting execution at 0xA0008000 use CTRL-C to interrupt.

>>> Start of sieves test. <<<

Sieve of Eratosthenes (scaled to 10 Iterations)

Array Size      Primes      Last Prime      BenchTime

(Bytes)        Found                  (Sec)

8191          1899          16381          0.060

10000          2261          19997          0.073

20000          4202          39989          0.149

40000          7836          79999          0.301

80000         14683         160001          0.610

160000         27607         319993          1.235

Relative to 10 Iterations and the 8191 Array Size:

Average BenchTime =      0.060 (sec)

>>> End of sieves test. <<<

Program Exit: 0

```

**Figure 2-1. Download Messages**

## 2.4.2 Terminal Emulation-to-Cyclone EP Communication Support

1. Invoke the terminal emulation program that you are using to communicate with the Cyclone EP.

2. To establish communication between the terminal emulation program and MON960, press <ENTER>. The MON960 prompt should appear. If it does not, press the RESET button.

3. When the MON960 prompt appears, enter **do** to download:

=> **do**

4. Start your terminal emulation program transfer mode and send SIEVE.XX. The following message displays when transfer completes:

-- Download complete --

Start address is: XXXXXXXX=>

5. To execute your program: at the MON960 prompt, enter **go**:

=> **go**

(**go** = go from start or continue from breakpoint)

The messages in Figure 2-2 display when the program completes (times may vary slightly). The example program has now been successfully compiled, assembled, linked, downloaded and executed.

```

>>> Start of sieves test. <<<

Sieve of Eratosthenes (scaled to 10 Iterations)

Array Size      Primes      Last Prime      BenchTime

(Bytes)        Found                  (Sec)

8191          1899          16381          0.060

10000          2261          19997          0.073

20000          4202          39989          0.149

40000          7836          79999          0.301

80000         14683         160001          0.610

160000         27607         319993          1.235

Relative to 10 Iterations and the 8191 Array Size:

Average BenchTime =      0.061 (sec)

>>> End of sieves test. <<<

Program Exit: 0

=>

```

Figure 2-2. Program Execution Messages

3

## HARDWARE REFERENCE

## CHAPTER 3

### HARDWARE REFERENCE

The location of the CPU and Squall modules, connectors, switches, and LEDs are described in this chapter. Also covered are the memory maps, I/O and memory operation. For the PCI-SDK Platform, this chapter describes the PCI 9060 interface and operation.

#### 3.1 CONNECTORS, SWITCHES AND LEDs

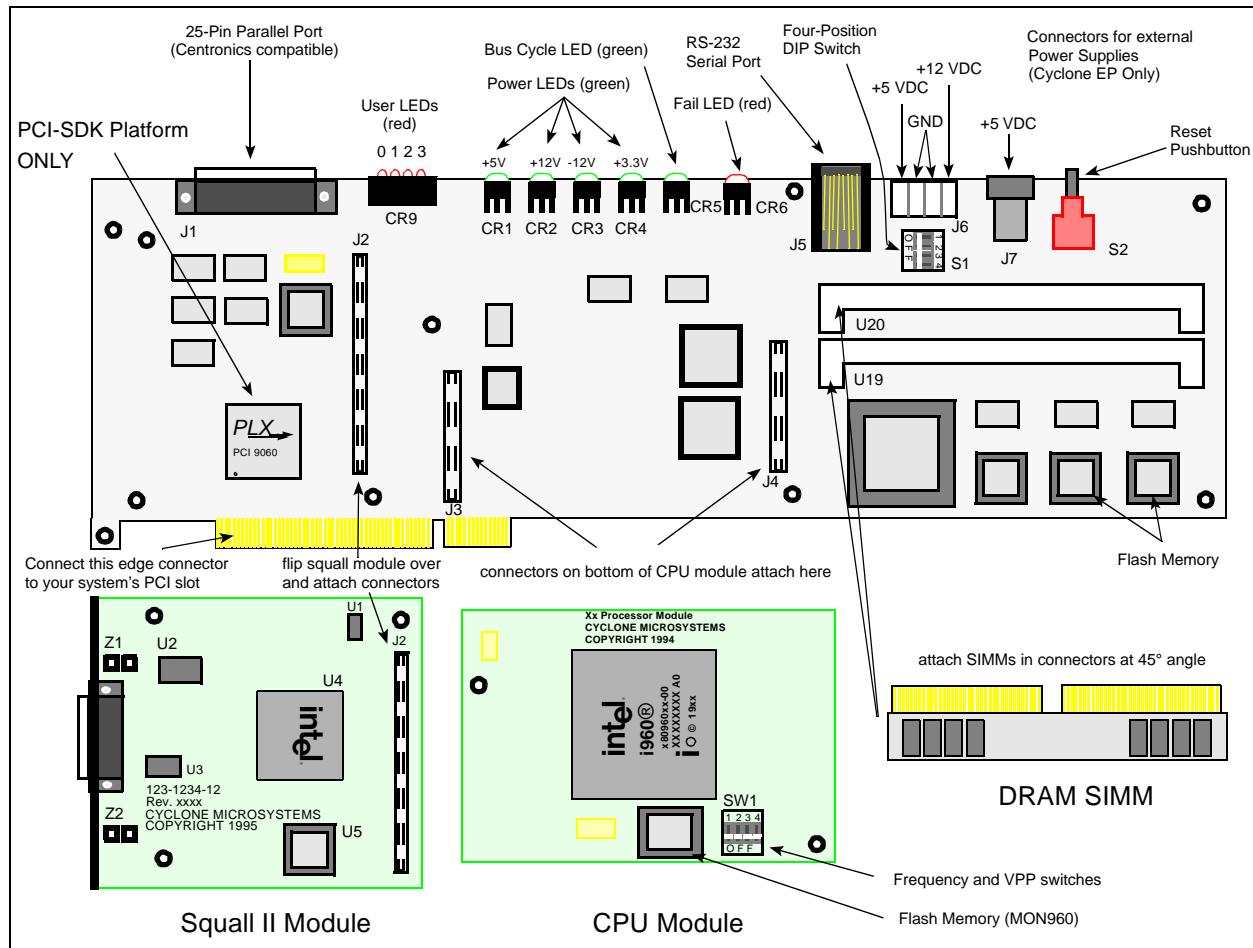

Figure 3-1 shows the physical location of the components you need to understand to use the Cyclone Evaluation Platform; Table 3-1 describes the function of each. For a complete list of components, refer to APPENDIX A, PARTS LIST.

Figure 3-1. Cyclone EP and PCI-SDK Platform Physical Diagram

Table 3-1. External Connectors and LEDs

| Function                                          | Ref.                            | Description                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power +5 VDC<br><b>(Cyclone EP only)</b>          | J7                              | A one-pin connector that interfaces to the primary power supply and cable (supplied). Provides +5 VDC and ground connections.<br>(On the PCI-SDK Platform, power is supplied through the edge connector.)                                                                                                                            |

| Power +5 VDC, +12 VDC<br><b>(Cyclone EP only)</b> | J6                              | A four-pin connector that interfaces to a secondary power supply and cable (not supplied). Three of the connector pins connect to +5 VDC, +12 VDC and ground.<br>(On the PCI-SDK Platform, power is supplied through the edge connector.)                                                                                            |

| LED (GREEN)                                       | CR1<br>CR2<br>CR3<br>CR4<br>CR5 | Lit when +5V is in tolerance<br>Lit when +12V is in tolerance<br>Lit when -12V is in tolerance<br>Lit when +3.3V and +5V is in tolerance<br>Lit when processor is performing bus cycles.                                                                                                                                             |

| LED (RED)                                         | CR6                             | Lit if processor fails self test or CPU module is not installed.                                                                                                                                                                                                                                                                     |

| User LEDs (RED)                                   | CR9                             | Four user-programmable LEDs; programmed via CIO Port C.                                                                                                                                                                                                                                                                              |

| Serial Port (RS-232)                              | J5                              | An RJ-11 ("phone plug") connector for serial communication and download.                                                                                                                                                                                                                                                             |

| Parallel Port<br>(Centronics-compatible)          | J1                              | A DB-25 connector for parallel download.                                                                                                                                                                                                                                                                                             |

| Squall II Interface                               | J2                              | Allows Squall II Module expansion. I/O devices are given direct access to the memory system.                                                                                                                                                                                                                                         |

| i960 Processor Module<br>(CPU Module)             | J3, J4                          | Modules which allow all current and future i960 processors to be used on the Cyclone EP and PCI-SDK Platform.                                                                                                                                                                                                                        |

| Four-position DIP Switch                          | S1                              | S1.1 Enables VPP to Cyclone EP base board Flash ROMs<br>S1.2 Enables UART Interrupt Request to the NMI<br>S1.3 ROMSWAP - causes the addresses of the CPU Module ROM and the base board ROMs to be exchanged. If switch is OFF the processor boots from the CPU Module ROM. If switch is ON the processor boots from base board ROMs. |

| Reset pushbutton                                  | S2                              | Used to manually reset the Cyclone EP.                                                                                                                                                                                                                                                                                               |

| DRAM SIMM Sockets                                 | U19-U20                         | Supports up to 32 Mbytes of standard 72-pin SIMMs.                                                                                                                                                                                                                                                                                   |

## 3.2 CPU MODULES

As shown in Figure 3-1, a CPU module is a smaller board that attaches directly onto the Cyclone EP. Several CPU modules are available — one for each member of the i960 processor family. Each module contains a i960 processor, boot Flash ROM with the MON960 monitor, appropriate glue logic and configuration switches.

### 3.2.1 CPU Module Installation

CPU modules are easy to install when a few guidelines are observed:

- Make sure the power is OFF before you install or remove a CPU module.

- Do not “peel” connectors. Peeling is the action of lifting one end of the connector before the other. This can bend or break the pins and connectors.

### 3.2.2 CPU Module Clock Frequencies

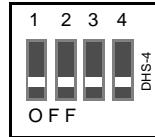

The CPU modules have user-assignable clock frequencies. Make sure you do NOT select a frequency faster than the installed processor is capable of running. Table 3-2 outlines the processor frequency switch settings. It is recommended that you remove power before you change the switch settings; however, if you change the switch settings while power is connected, press the reset switch to reboot the processor at the new frequency.

**NOTE:**

**DO NOT** select a frequency faster than the installed processor is capable of running.

**Table 3-2. CPU Module Frequency Switch Settings**

| Frequency | FREQ2<br>(Pos2) | FREQ1<br>(Pos3) | FREQ0<br>(Pos4) | Switch Diagram <sup>1,2</sup>                                                                  |

|-----------|-----------------|-----------------|-----------------|------------------------------------------------------------------------------------------------|

| 16 MHz    | ON              | OFF             | ON              | <br>DHS-4 |

| 20 MHz    | ON              | OFF             | OFF             |                                                                                                |

| 25 MHz    | OFF             | ON              | ON              |                                                                                                |

| 33 MHz    | OFF             | ON              | OFF             |                                                                                                |

| 40 MHz    | OFF             | OFF             | ON              |                                                                                                |

| 50 MHz    | OFF             | OFF             | OFF             |                                                                                                |

**NOTES:**

1. On the 80960Sx and Kx CPU Modules, the CPU Module Frequency Switch is labeled SW2. On all other 80960 CPU Modules, the CPU Module Frequency Switch is labeled SW1.

2. CPU module switch position 1 (Pos1) is the V<sub>PP</sub> switch. It is recommended that you leave it OFF. (Factory default position.)

### 3.2.3 i960 Jx/Hx CPU Counter/Timers

The i960 Jx and Hx processors are equipped with two on-chip counter/timers. These timers are clocked at the CPU clock rate which does not correspond exactly with the CPU Module Frequency Switch settings. Use Table 3-3 to determine the exact CPU clock frequency.

**Table 3-3. i960 Jx/Hx CPU Clock Rates**

| CPU Frequency Switch Setting | CPU Clock Frequency |

|------------------------------|---------------------|

| 16 MHz                       | 16.11 MHz           |

| 20 MHz                       | 20.05 MHz           |

| 25 MHz                       | 25.06 MHz           |

| 33 MHz                       | 33.41 MHz           |

| 40 MHz                       | 40.09 MHz           |

### 3.2.4 CPU Module V<sub>PP</sub> Switch

The V<sub>PP</sub> Switch (switch position 1 in Table 3-2) enables/disables V<sub>PP</sub> to the boot Flash ROMs located on the CPU module. It is recommended that this switch remains set to OFF (the default setting from the factory). When V<sub>PP</sub> is enabled (switch in ON position), the processor may not be able to boot from ROM if the power sequencing of +5V and +12V is not correct.

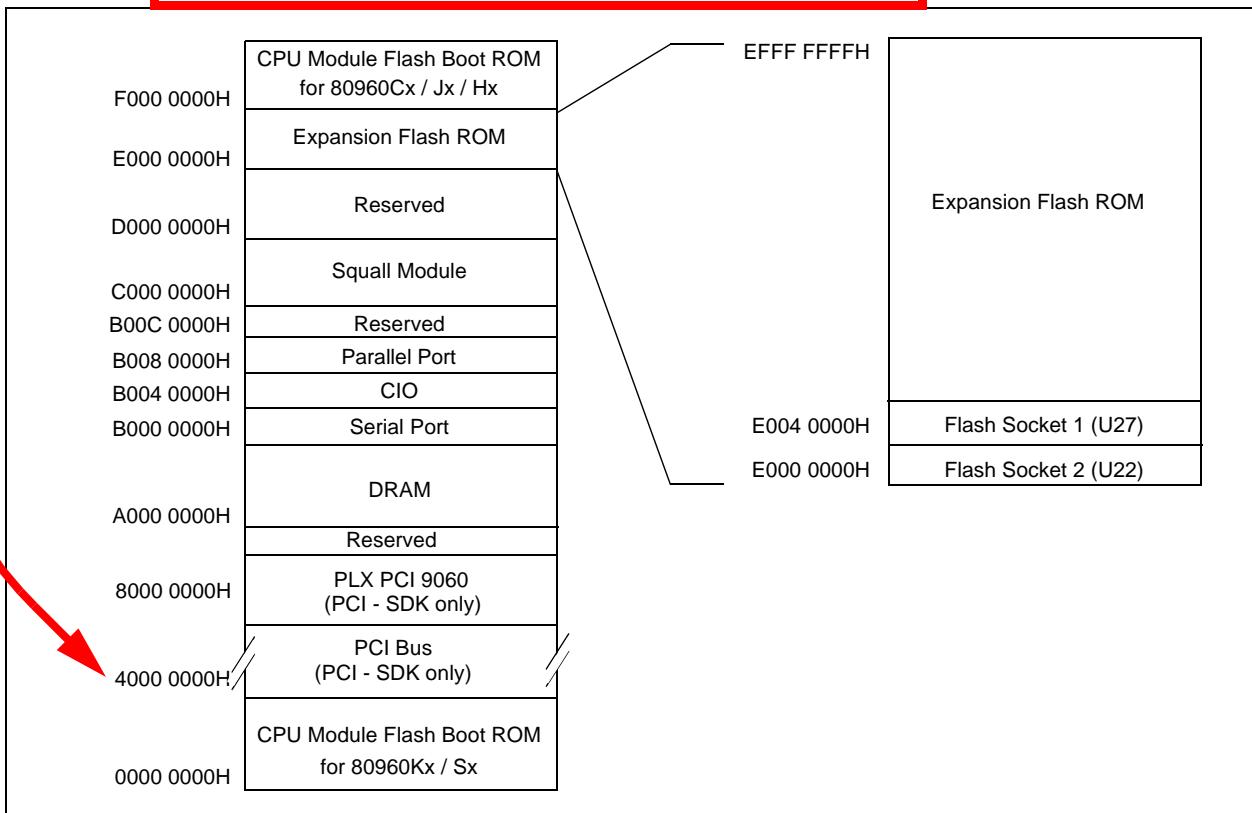

## 3.3 CPU MEMORY MAP

As indicated in Figure 3-2, the memory map is organized to take advantage of the i960 Cx, Hx, and Jx processors' bus sizing capabilities. Memories and I/O devices are described in the sections following the figure.

Figure 3-2, DRAM Memory Map for Cyclone EP, incorrectly showed the PCI Bus Address as 1000 0000H. It now correctly shows 4000 0000H.

**Figure 3-2. DRAM Memory Map for Cyclone EP**

### 3.4

#### INTERLEAVED DRAM

The Cyclone EP is initially configured with 2 Mbytes of interleaved DRAM. This memory, located in the SIMM sockets, is upgradeable to 8 or 32 Mbytes. Figure 3-1 (pg. 3-1) shows the SIMMs and sockets. Section 3.4.2 discusses the DRAM configuration options.

Access to this DRAM can be shared with the Squall II Module I/O device's DMA controller. A priority arbitration circuit ensures that only one device is using the memory at a time.

#### 3.4.1

##### DRAM Performance

The DRAM controller automatically adjusts wait states based on processor type, processor clock frequency, and memory speed. The controller supports burst transfers using the interleaved banks to maximize performance. Table 3-4 lists DRAM performance.

The default memory configuration uses 70 ns memory. At processor frequencies of 25 and 40 MHz, wait states are reduced using 60 ns memory.

**Table 3-4. DRAM Access Times**

| Frequency | Operation | DRAM Speed | Clock Cycles           | Wait States | Sustained Bandwidth <sup>1</sup> |

|-----------|-----------|------------|------------------------|-------------|----------------------------------|

| 16 MHz    | Read      | 60, 70ns   | 3,1,1,1                | 1,0,0,0     | 36 Mbytes/sec                    |

| 20 MHz    | Read      | 60, 70ns   | 3,1,1,1                | 1,0,0,0     | 45 Mbytes/sec                    |

| 25 MHz    | Read      | 60ns       | 3,1,1,1                | 1,0,0,0     | 66 Mbytes/sec                    |

| 25 MHz    | Read      | 70ns       | 4,1,1,1,1 <sup>2</sup> | 2,0,0,0     | 50 Mbytes/sec                    |

| 33 MHz    | Read      | 60, 70ns   | 4,1,1,1,1 <sup>2</sup> | 2,0,0,0     | 66 Mbytes/sec                    |

| 40 MHz    | Read      | 60ns       | 4,1,1,1,1 <sup>2</sup> | 2,0,0,0     | 80 Mbytes/sec                    |

| 40 MHz    | Read      | 70ns       | 5,2,2,2,1 <sup>2</sup> | 3,1,1,1     | 53 Mbytes/sec                    |

| 16 MHz    | Write     | 60, 70ns   | 3,2,2,2                | 1,1,1,1     | 25.6 Mbytes/sec                  |

| 20 MHz    | Write     | 60, 70ns   | 3,2,2,2                | 1,1,1,1     | 32 Mbytes/sec                    |

| 25 MHz    | Write     | 60ns       | 3,2,2,2                | 1,1,1,1     | 44.5 Mbytes/sec                  |

| 25 MHz    | Write     | 70ns       | 4,2,2,2,1 <sup>2</sup> | 2,1,1,1     | 36 Mbytes/sec                    |

| 33 MHz    | Write     | 60, 70ns   | 4,2,2,2,1 <sup>2</sup> | 2,1,1,1     | 48 Mbytes/sec                    |

| 40 MHz    | Write     | 60ns       | 4,2,2,2,1 <sup>2</sup> | 2,1,1,1     | 58 Mbytes/sec                    |

| 40 MHz    | Write     | 70ns       | 4,2,2,2,1 <sup>2</sup> | 2,1,1,1     | 58 Mbytes/sec                    |

**NOTES:**

1. Bandwidths stated are sustained bandwidths, not peak.

2. The extra cycle is the overhead of DRAM precharge. DRAM precharge time only impacts back-to-back cycles.

### 3.4.2 Upgrading SIMM DRAM

On-board DRAM is located in two SIMM sockets as shown in Figure 3-1 (pg. 3-1). The standard configuration is 2 Mbytes of memory and may be upgraded to 8 or 32 Mbytes. Table 3-5 shows the modules which you may use. The memory modules should use 60 or 70 ns Fast Page Mode DRAM (60 ns memory results in better performance at 25 and 40 MHz operation). Use fast page mode, x32 or x36, 72 pin SIMMs.

The SIMM block consists of two standard 72-pin SIMM sockets, arranged as two banks. Both SIMM sockets must contain SIMMs; these cannot be left empty. The sockets accept the following SIMM types.

- 256 Kbyte x 32 = 1 Mbyte

- 1 Mbyte x 32 = 4 Mbyte

- 4 Mbyte x 32 = 16 Mbyte

- 256 Kbyte x 36 = 1 Mbyte

- 1 Mbyte x 36 = 4 Mbyte

- 4 Mbyte x 36 = 16 Mbyte

The x36 SIMM parity bits are not used in this design. However, the x36 SIMMs are standard for PCs and workstations, which makes them more readily available. The only penalty is more loading on the address and control lines due to the extra DRAM devices on the x36 SIMM.

All address and control lines to the SIMMs are terminated with 22 ohm resistors.

**Table 3-5. DRAM SIMM Configurations**

| Total Memory (both modules) | Module Type         |

|-----------------------------|---------------------|

| 2 Mbytes                    | 256K x 32 (1 Mbyte) |

| 8 Mbytes                    | 1M x 32 (4 Mbytes)  |

| 32 Mbytes                   | 4M x 32 (16 Mbytes) |

**NOTE:**

Both SIMM modules must be installed; SIMM sockets cannot be empty.

The board has no shunts or switches to change for a memory upgrade. Memory speed is indicated by the Presence Detect Signals; the DRAM controller automatically adjusts to minimum wait states for the processor frequency and memory speeds. The initialization code automatically sizes the memory so user software can take advantage of larger memory modules.

**3.5****FLASH MEMORY**

The Cyclone EP provides two banks of Flash memory: a primary memory bank on the CPU module and an expansion bank on the base board. The default configuration of this memory is as the boot memory containing the MON960 monitor. The second bank of memory is two sockets for Intel 28F020 devices (Intel part number N28F020-200) in locations U22 and U27. These memory devices may be used for user application code, or using the SwapROM switch, as boot memory.

**3.5.1****SwapROM Switch**

The SwapROM switch (third switch on SW1) exchanges the addresses of the CPU module boot ROM and the expansion ROMs to allow the processor to boot from the expansion ROM. Table 3-6 shows the address of the Flash ROMs relative to the SwapROM switch. Figure 3-1 shows SW1 switch location.

**NOTE:**

This feature is supported for all i960 processors except for Kx and Sx processors. These must boot from boot ROMs and, therefore, must have the SwapROM switch set to OFF.

**Table 3-6. Flash ROM Addresses**

| ROM Type             | SwapROM Switch OFF | SwapROM Switch ON |

|----------------------|--------------------|-------------------|

| CPU Module Boot ROM  | F000 0000H         | E000 0000H        |

| Expansion ROM0 (U22) | E000 0000H         | F000 0000H        |

| Expansion ROM1 (U27) | E004 0000H         | F004 0000H        |

If a single Expansion ROM is used as a Boot ROM, use location U27 (ROM1) so the i960 processor finds the IBR at the top of the memory map.

### 3.6 INTERRUPTS

The Cyclone EP has seven interrupt sources. The CPU module assumes the interrupts are direct mapped. Table 3-7 lists the interrupt sources and the corresponding  $\overline{XINT}$  signals. All interrupts are level sensitive except the Squall II Module IRQ0 and IRQ1; these are dependent on the particular Squall II Module installed.

**Table 3-7. Interrupt Sources**

| XINT Signal | Interrupt Source       |

|-------------|------------------------|

| XINT0       | PLX PCI 9060           |

| XINT1       | Parallel Port          |

| XINT2       | PCI 9060 LSERR         |

| XINT3       | Deadlock Error         |

| XINT4       | Squall II Module IRQ0  |

| XINT5       | Squall II Module IRQ1  |

| XINT6       | Counter/Timers (Z8536) |

| XINT7       | Serial Port (16C550)   |

The Sx and Kx processors have only four dedicated interrupt signals. A dip switch is provided on the Sx and Kx CPU modules to map the six possible interrupt sources to the four direct mapped interrupt inputs. Table 3-8 outlines the interrupt mapping for the Sx and Kx CPU modules.

The interrupt sources to INT1 and INT2 are selected using SW-1 on Sx and Kx modules. Table 3-9 shows all valid combinations. Positions 1 and 2 select the interrupt source to INT1 and both cannot be ON or OFF simultaneously. Likewise, positions 3 and 4 select the interrupt source to INT2 and both cannot be ON or OFF simultaneously.

**Table 3-8. 80960Sx and Kx Interrupt Sources**

| INT Signal | Interrupt Source                                   |

|------------|----------------------------------------------------|

| INT0       | Counter/Timers (Z8536)                             |

| INT1       | Serial Port UART (16C550) or Squall II Module IRQ1 |

| INT2       | Parallel Port or PLX PCI 9060                      |

| INT3       | Squall II Module IRQ0                              |

Table 3-9. 80960Sx and Kx Interrupt Switch Settings

| Interrupt Source                          | Pos1       | Pos2        | Pos3        | Pos4       | Switch Diagram |

|-------------------------------------------|------------|-------------|-------------|------------|----------------|

| Serial Port UART<br>PLX PCI 9060          | <b>ON*</b> | <b>OFF*</b> | <b>OFF*</b> | <b>ON*</b> |                |

| Squall II Module<br>IRQ1<br>PLX PCI 9060  | OFF        | ON          | <b>OFF*</b> | <b>ON*</b> |                |

| Serial Port UART<br>Parallel Port         | <b>ON*</b> | <b>OFF*</b> | ON          | OFF        |                |

| Squall II Module<br>IRQ1<br>Parallel Port | OFF        | ON          | ON          | OFF        |                |

**NOTE:**

\* Bold indicates factory default position

### 3.7 CONSOLE SERIAL PORT

The Cyclone EP has a single console port with an RS-232 line interface. The port uses a phone plug connector, and the board is supplied with a phone jack to DB25 cable.

The serial port is implemented with a 16C550 UART clocked with a 1.843 MHz clock. The device may be programmed to use this clock with the internal baud rate counters. The serial port may be run at baud rates between 1200 and 115200 baud. Refer to the 16C550 device data book for a detailed description of the registers and device operation.

Table 3-10. UART Register Addresses

| Address    | Read Register             | Write Register                                                      |

|------------|---------------------------|---------------------------------------------------------------------|

| B000 0000H | Receive Holding Register  | Transmit Holding Register                                           |

| B000 0004H | Unused                    | Interrupt Enable Register                                           |

| B000 0008H | Interrupt Status Register | FIFO Control Register                                               |

| B000 000CH | Unused                    | Line Control Register                                               |

| B000 0010H | Unused                    | Modem Control Register                                              |

| B000 0014H | Line Status Register      | Unused                                                              |

| B000 0018H | Modem Status Register     | Unused                                                              |

| B000 001CH | Scratchpad Register       | Scratchpad Register<br>LSB of Divisor Latch<br>MSB of Divisor Latch |

### 3.8 PARALLEL PORT

A Centronics PC-compatible receive-only parallel port is implemented on the Cyclone EP. You access and control the parallel port by using three memory-mapped registers (see Table 3-11):

- Parallel port data register

- Parallel port status register

- Parallel port control register

The port uses a DB25 connector with PC-compatible pin assignments. A cable is included with the Cyclone EP to facilitate downloading of code from a host development workstation or PC.

**Table 3-11. Parallel Port Addresses**

| Address    | Read Register   | Write Register   |

|------------|-----------------|------------------|

| B008 0000H | Status Register | Control Register |

| B008 0004H | Data Register   | Unused           |

#### 3.8.1 Parallel Port Bit Assignments

Table 3-12 shows the read-only parallel port status register bit assignments.

**Table 3-12. Parallel Port Status Register Bit Assignments**

| Bit | Signal Mnemonic | Signal Name     |

|-----|-----------------|-----------------|

| 7   | not used        | —               |

| 6   | not used        | —               |

| 5   | BUSY            | Bus Busy        |

| 4   | ACK             | Acknowledge     |

| 3   | PPSLCTIN        | Select In       |

| 2   | PPFEED          | Paper Feed      |

| 1   | PSTROBE         | Data Strobe     |

| 0   | PPINIT          | Port Initialize |

The parallel port control register is a write-only 8-bit register that controls parallel port operation. This register also contains an interrupt enable bit (PINTEN) that enables the parallel port interrupt. When the interrupt is enabled, an interrupt is signaled when either  $\overline{PSTROBE}$  or  $\overline{PPINIT}$  is asserted. The interrupt is cleared when the parallel port data register is read. Table 3-12 shows the parallel port control register.

**Table 3-13. Parallel Port Control Register Bit Assignments**

| Bit | Signal Mnemonic | Signal Name      |

|-----|-----------------|------------------|

| 7   | not used        | —                |

| 6   | not used        | —                |

| 5   | not used        | —                |

| 4   | BUSY_CTRL       | Busy Control     |

| 3   | PINTEN          | Enable Interrupt |

| 2   | PPOUT           | Paper Out        |

| 1   | PPSEL           | Select Out       |

| 0   | PPERR           | Error Output     |

### 3.9 Z8536 COUNTER I/O UNIT (CIO)

The Z8536 device performs several functions on the Cyclone EP. The device provides three 16-bit counter/timers that may be used to generate interrupts or count events. The CIO generates interrupts on the processor's  $\overline{XINT6}$  signal. The CIO also contains three parallel ports which are used for on-board control and status such as reading and writing the on-board and Squall Module EEPROMs, and to read the board's configuration. The following subsections outline the Cyclone EP's specific usage of the CIO. For detailed programming instructions, refer to the Zilog Z8536 Technical Manual.

**Table 3-14. CIO Register Address**

| Register             | Address    | Description                 |

|----------------------|------------|-----------------------------|

| Port C Data          | B004 0000H | User LEDs                   |

| Port B Data          | B004 0004H | EEPROM Clock & Data         |

| Port A Data          | B004 0008H | Control Bits                |

| CIO Control Register | B004 000CH | CIO Configuration & Control |

#### 3.9.1 Counter/Timers

Three 16-bit counter/timers can be used to generate interrupts on the processor's  $\overline{XINT6}$  signal. Counters 1 and 2 can be linked internally to provide a 32-bit counter for longer timing sequences. The CIO is clocked with a 4.000 MHz ( $\pm 0.01\%$ ) clock. Internally, this signal is divided by 2, which actually clocks the counters with a 2.000 MHz clock. Example code for using the counter/timers may be found in the MON960 Board Test (bt) code.

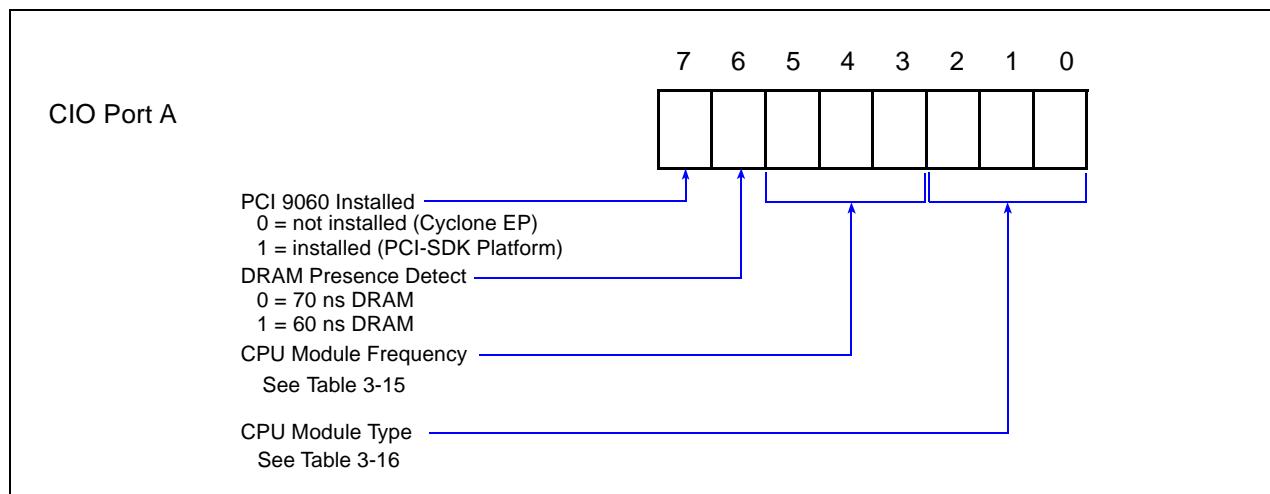

### 3.9.2 CIO Port A

Port A, an 8-bit input port, is used to report CPU and memory module configuration:

- Bits 0-2 report the CPU module processor type.

- Bits 3-5 report on the selected CPU module frequency.

- Bit 6 reports on the speed of the installed DRAM.

- Bit 7 is the PCI 9060 Installed Bit.

Example code for initializing and reading this register is located in the initialization portion of the MON960.

Figure 3-3 shows the bits and bit definitions; tables following the figure define the bit functions.

Figure 3-3. CIO Port A

Table 3-15. CIO Port A Bits 5-3

| Frequency | CPU Module Frequency Signals |

|-----------|------------------------------|

| 16 MHz    | 010                          |

| 20 MHz    | 011                          |

| 25 MHz    | 100                          |

| 33 MHz    | 101                          |

| 40 MHz    | 110                          |

**Table 3-16. CIO Port A Bits 2-0**

| Module Type           | CPU Module Type Signals |

|-----------------------|-------------------------|

| 80960Sx               | 000                     |

| 80960Kx               | 001                     |

| 80960Cx               | 010                     |

| 80960Hx               | 011                     |

| 80960Jx               | 100                     |

| Reserved <sup>1</sup> | 101                     |

| Reserved <sup>1</sup> | 110                     |

| Reserved <sup>1</sup> | 111                     |

**NOTE:**

1. Reserved for future processors

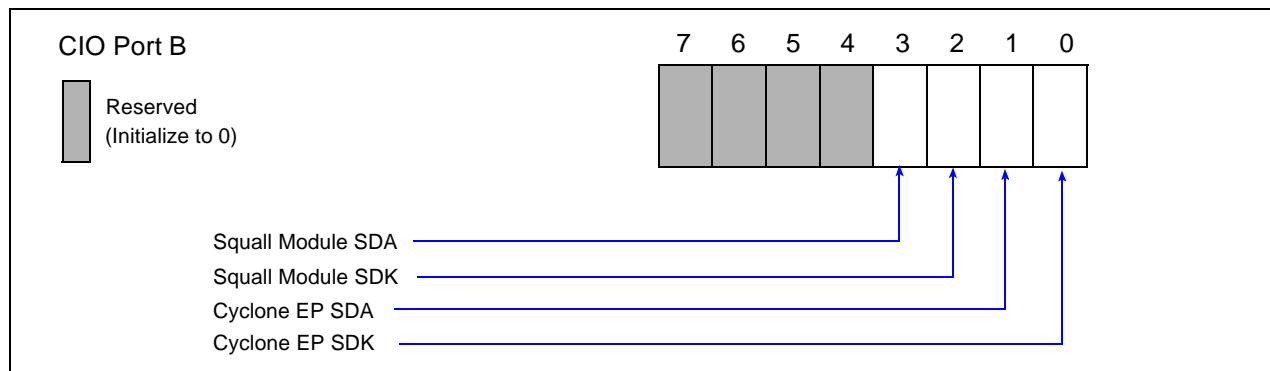

### 3.9.3 CIO Port B

Port B is an 8-bit I/O port used to clock, read and write the serial EEPROMs located on the Cyclone EP and the Squall II Module. Configure the port as open collector bidirectional pins. Figure 3-4 shows the pin assignments. Section 5.3, Squall II Module Serial EEPROM (pg. 5-3) discusses the serial EEPROMs and reserved data fields. Cyclone Microsystems has written code to read and write the serial EEPROMs, which is included in the initialization portion of the MON960.

**Figure 3-4. CIO Port B**

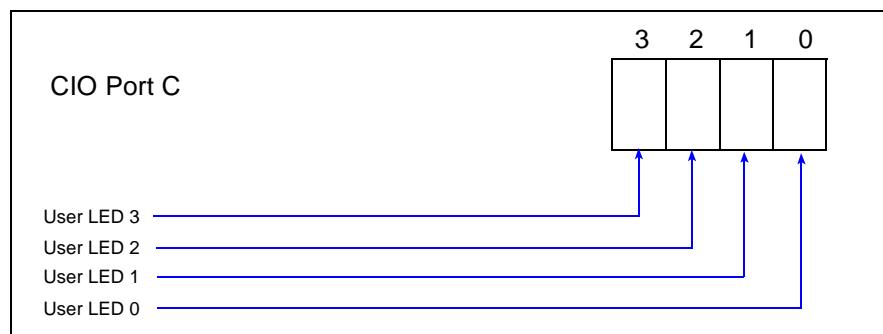

### 3.9.4 CIO Port C

Port C is a 4-bit output-only port used to drive the four User LEDs (CR9) on the Cyclone EP. These LEDs are provided as an aid in debugging. As shown in Figure 3-1, the leftmost LED is LED 0, which corresponds to CIO Port C bit 0; the rightmost LED is LED 3, which corresponds to CIO Port C bit 3. Setting bits (writing a 1) in CIO Port C register turns ON the corresponding LED; clearing bits (writing a 0) turns the LEDs OFF.

**Figure 3-5. CIO Port C**

### 3.10 NON-VOLATILE PARAMETER MEMORY

The Cyclone EP has a 1 Kbyte x8 EEPROM memory which may be used for storing operating system and other default parameters. The memory is read and written in a serial fashion using Port B of the CIO (Z8536). (Refer to a Xicor, Inc. 24C08 data sheet for technical information.) Cyclone has written routines to access these devices; the routines are included in the initialization portion of MON960.

Like the 24C08 EEPROM on every Squall II Module, bytes are read from and written to the EEPROM's most significant bit (bit 7) first and least significant bit (bit 0) last. The contents of the on-board EEPROM are not defined by Cyclone. User software may use this storage for any purpose, although it is intended for non-volatile storage of an operating system's boot parameters. Real-time kernels, such as VxWorks\* and pSOSSystem\*, use this memory for the storage of boot parameters.

### 3.11 SQUALL II MODULE INTERFACE

The Cyclone EP contains a single Squall II Module expansion location and connector. Cyclone Microsystems has many off-the-shelf modules available; users are also encouraged to build their own modules. Chapter 5 contains complete electrical and mechanical specifications of the Squall II Module. Table 3-17 lists the Squall II Modules currently available from Cyclone Microsystems. Table 3-18 shows the i960 CPU / Squall module compatibility.

See Section 1.4, ADDITIONAL INFORMATION (pg. 1-4) for information on how to contact Cyclone Microsystems. They are continually developing new modules and will consider the development of custom modules.

Table 3-17. Available Squall II Modules

| Module | Description                                            |

|--------|--------------------------------------------------------|

| SQ01   | Ethernet (82596CA)                                     |

| SQ10   | SCSI-2 (NCR 53C710)                                    |

| SQ11   | SCSI-2 Wide (NCR 53C720)                               |

| SQ20   | High Speed Serial with DMA; Two RS-422 (Hitachi 64570) |

| SQ40   | Parallel Input with Differential Receivers             |

Table 3-18. Squall Module Compatibility at Maximum CPU Clock Speed (33 MHz)

| CPU Type | SQ01             | SQ10            | SQ11            | SQ20            | SQ40 |

|----------|------------------|-----------------|-----------------|-----------------|------|

| 80960Sx  | YES <sup>1</sup> | NO <sup>2</sup> | NO <sup>2</sup> | NO <sup>3</sup> | NO   |

| 80960Kx  | YES <sup>1</sup> | YES             | YES             | NO <sup>4</sup> | YES  |

| 80960Cx  | YES              | YES             | YES             | YES             | YES  |

| 80960Jx  | YES              | YES             | YES             | YES             | YES  |

| 80960Hx  | YES              | YES             | YES             | YES             | YES  |

**NOTES:**